[! note] 这一章前面的 MOS 的静态特性又把第一章的内容重复了一遍,如果要更结构化的推荐看 《Chapter 2 硅 MOSFET 》笔记。这一章后面的部分从教材 ref 处开始。

[! reference] “动态特性” (拉贝艾, 2010, p. 71)

1. 动态特性

MOSFET 的动态响应取决于器件的本征寄生电容和互联线以及负载引起的额外电容。这一节我们关注器件的本征寄生电容的构成,主要是 MOS 结构电容,沟道电容和结电容。

1.1. MOS 结构电容

MOS 本身的栅极结构就构成了其 MOS 结构电容。前面在计算 MOS 线性工作时的漏极电流的时候,就已经定义了栅氧单位面积电容

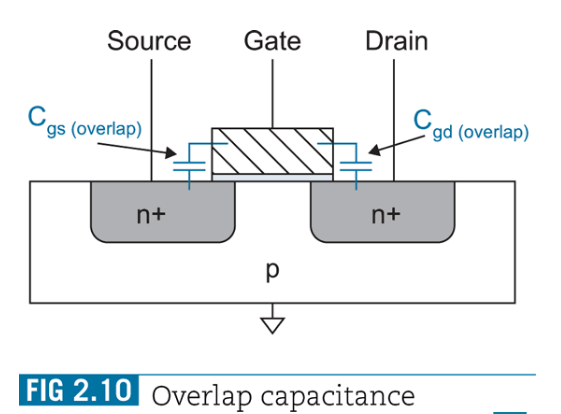

1.1.1. 覆盖电容

理想情况下,源和漏的扩散应该恰好终止在栅氧边上,但是实际上都会往氧化层下延展

覆盖电容是线性的且具有固定的值,典型值为

覆盖电容计算式

指向原始笔记的链接

为栅源覆盖电容; 为栅漏覆盖电容; 为栅氧单位面积电容; 为横向扩散量; 为晶体管宽度; 为每单位晶体管覆盖电容。

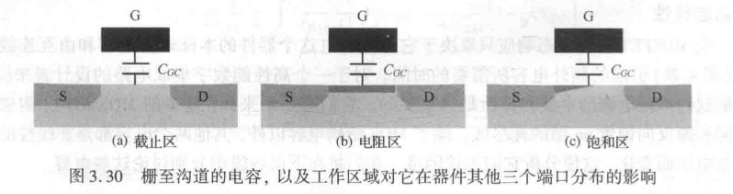

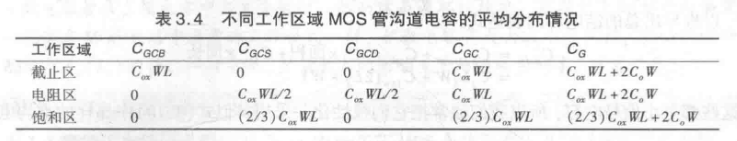

1.2. 沟道电容

栅至沟道电容  当晶体管截止的时候,栅至沟道电容主要由

当晶体管截止的时候,栅至沟道电容主要由

可以看出来,随着饱和程度的增加总的栅电容逐渐变小。

1.2.1. 总结

总的栅极电容

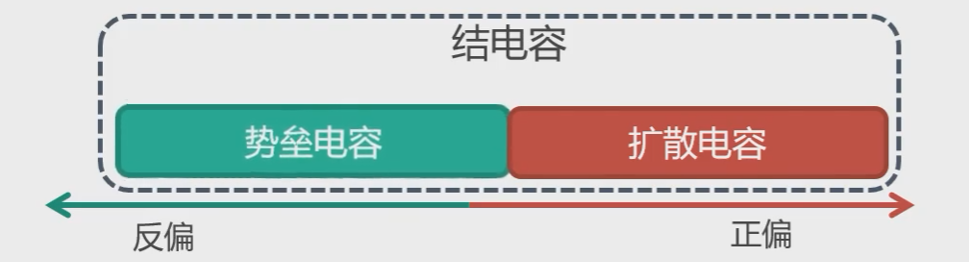

1.3. 结电容

结电容(

每单位面积结电容

每单位面积结电容由以下公式给出,

有内建电势为,

pn 结内建电势差计算式

指向原始笔记的链接

为玻尔兹曼常数; 是 pn 结的绝对温度; 是电子电荷; 为受主掺杂浓度; 为施主掺杂浓度; 为本征载流子浓度

每单位周长结电容由以下公式给出,

参数的含意和每单位面积结电容类似。

2. 非理想 I-V 特性

2.1. MOS 二阶效应

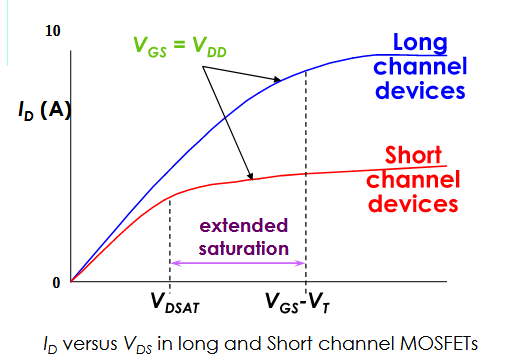

当沟道的长度缩短到能够和其他的器件相比较的时候,这个器件就成了短沟道晶体管,不能再考虑为一个理想的器件。当分析短沟道晶体管的时候,需要用 2D 模型。

2.1.1. 速度饱和效应

在实际情况中,随着

- 在高横向场强(

)下,载流子速度不再随场强线性增加。这称为速度饱和,在高 下会导致 低于预期。 - 在高垂直场强 (

) 下,载流子更频繁地散射。这种迁移率降低效应还会导致高 下的电流低于预期。

非理想晶体管的饱和电流随

对于速度饱和,

对于短沟道器件,

理想的晶体管开启电流,

如果再考虑速度饱和的话,

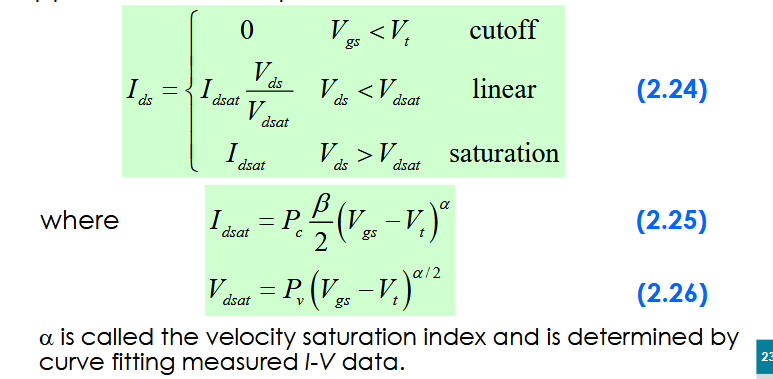

2.1.2.

对于中等电源电压,晶体管工作在速度不再随场线性增加但也未完全饱和的区域 (就是从线性区到饱和区之间的过渡区)。方程中给出的 α-幂律模型。 (2.24) 提供了一个简单的近似来捕捉这种行为。

[! note] 这个

幂率模型感觉就是个曲线拟合,实际意义不大。

2.1.3. 等效电阻

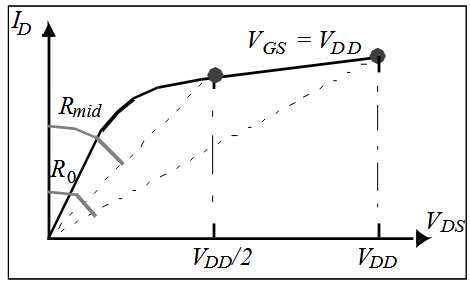

当我们将 MOS 建模为简单开关模型的时候,会将 MOS 考虑为一个开关和一个电阻的串联。这里的等效电阻,就是在考虑沟道长度调制效应的基础上,取

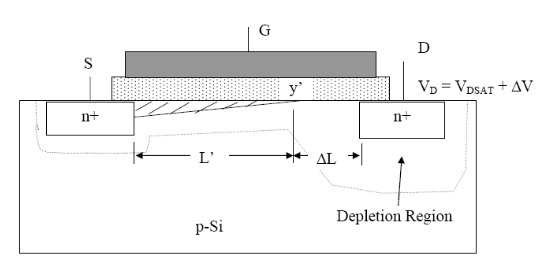

2.1.4. 沟道长度调制效应

沟道长度调制效应

当

的时候,沟道的长度 因为漏极和衬底之间的耗尽区的扩展而逐渐缩小为 。引入沟道长度调制系数来表征。这个效应会导致晶体管的饱和电流 随 缓慢线性增加,从而导致了高输出电导。

沟道长度调制效应耗尽层增量计算式

指向原始笔记的链接 指向原始笔记的链接沟道长度调制系数

为了代表漏源电压对于漏极电流的调制而引入的一个较小的经验系数

指向原始笔记的链接,这个系数就是沟道长度调制系数。这个系数的加入使得沟道长度调制效应得以用物理公式来解释。

2.1.5. 体效应

体效应

体效应是指,当 NMOS 源端电势大于衬底电势(

)时,栅下面的表面层中将有更多的空穴被吸收到衬底上 (因为此时相对而言衬底更负),留下更多不能移动的负离子(负电中心),使得耗尽层展宽。阈值电压升高。 体效应系数

体效应系数

指向原始笔记的链接

为氧化层厚度; 为氧化层介电常数; 电子电荷绝对值; 硅的介电常数; 衬底区域的杂志浓度; 氧化层的电容密度; 对于 NMOS 而言为正,对 PMOS 而言为负。 阈值表面电压

阈值表面电压就是刚刚开始耗尽层刚刚开始反型的时候的栅极电压。阈值表面电压计算式

指向原始笔记的链接

为 p 型硅衬底费米势。 体效应修正的阈值电压

指向原始笔记的链接阈值电压计算式

指向原始笔记的链接

为零偏置阈值电压; 为体效应系数; 为阈值表面电压; 为源衬电势差。

2.1.6. 亚阈值传导

亚阈值漏电

当栅极电压略小于阈值电压(

),但是没有完全使得沟道反相的时候,仍然有电流流过,这就是亚阈值漏电。 源极和漏极是反向偏置二极管,也会经历结泄漏到衬底或阱中。进入栅极的电流

指向原始笔记的链接理想情况下为 0。然而,随着栅极氧化物的厚度减小到只有少量原子层,电子会隧道穿过栅极,从而产生一些栅极电流。

亚阈值斜率计算式,

亚阈值泄露电流是

有阈值电流,

器件的增益系数计算式

指向原始笔记的链接

亚阈值传导在极低功耗模拟电路中具有优势。对于动态电路和 DRAM 来说也特别重要,因为这取决于电容器上的电荷存储。定期刷新旨在应对晶体管关闭时发生的泄漏。

漏电也会导致空闲电路中的功耗。随着 Vt 降低或温度升高,漏电呈指数增加,因此对于使用低电源和阈值电压的芯片来说,漏电正成为一个主要问题。

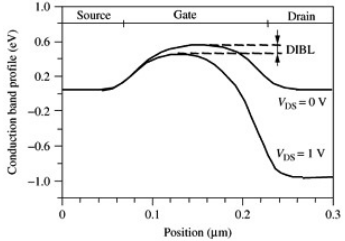

2.1.7. 漏极诱导势垒降低 (DIBL)

漏极感应势垒降低 (DIBL) 会加剧亚阈值传导,其中正 Vds 会有效降低 Vt。也就是说,漏极电压也会影响 Vt,其中高漏极电压会导致亚阈值泄漏增加。

这种效应在漏极更靠近沟道的短沟道晶体管中尤其明显。降低后的势垒值为,

通过提高 VDS(体)电压,漏极结耗尽区的宽度会增加,并且 VT 会随着 VDS 的增加而降低。这种效应称为漏极感应势垒降低 (DIBL),导致 VT 成为工作电压的函数。如果 VD 足够高,源极和漏极区域甚至可以短接在一起。当这种情况发生时,晶体管停止正常工作,因此发生了穿通。

通过提高 VDS(体)电压,漏极结耗尽区的宽度会增加,并且 VT 会随着 VDS 的增加而降低。这种效应称为漏极感应势垒降低 (DIBL),导致 VT 成为工作电压的函数。如果 VD 足够高,源极和漏极区域甚至可以短接在一起。当这种情况发生时,晶体管停止正常工作,因此发生了穿通。

在数字电路中,大多数晶体管都是按最小沟道长度设计的。因此,VT 作为长度函数的变化在整个设计中几乎是一致的,并且是次要问题。更令人担忧的是 DIBL 随工作电压的变化而变化。这在动态存储器中是一个问题,其中单元的漏电流(即存取晶体管的亚阈值电流)成为数据线上电压的函数,该电压与许多其他单元共享。除了随设计而变化之外,短沟道器件中的 VT 还由于热载流子效应而具有随时间漂移的趋势。

2.1.7.1. 由于尺寸缩小而导致电场增加

在过去的几十年里,设备尺寸已大大缩小,但电源和工作电压或多或少保持恒定。由此产生的电场强度增加导致电子速度增加,这可能导致它们在达到足够高的能级时离开硅并隧道进入栅极氧化物。氧化物中捕获的电子会改变 VT,通常会增加 NMOS 器件的 VT,同时降低 PMOS 晶体管的 VT。

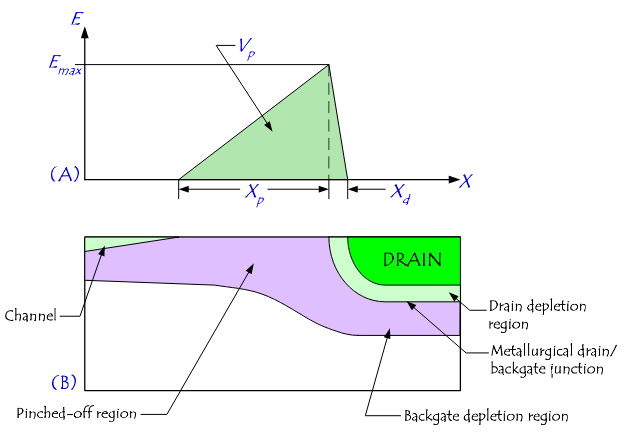

2.1.7.2. 横向电场

场强在夹断区域内线性上升,并在漏极冶金结处达到最大值。然后,场在漏极内部的耗尽区上线性下降。

从源到漏的总电压为,

最大电场强度 Emax 和夹断区域 xp 的宽度分别受到热载流子产生和沟道长度调制的限制。增加工作电压 VDS 的唯一方法是增加耗尽区 xd 的宽度。这又需要更轻掺杂的漏极,但轻掺杂漏极也是高电阻漏极。于是一般采取的方法是,在漏极处,沿着沟道增加一部分轻掺杂的区域,用来增加

2.1.7.3. 热载流子效应

电子要变热,至少

热载流子注入和表面效应

高电场强度的表面区域可以将热载流子注入上面的氧化物中。 表面电场也会诱发寄生通道的形成。这两种机制都被称为表面效应,因为它们发生在硅和上覆氧化物之间的界面处。

热载流子注入的影响

在大 VDS 下,沿着沟道从源极流向漏极的电子会遇到强电场,从而在夹断区域将它们加速到高速。由此产生的热电子撞击晶格原子并以各个角度弹开, 部分注入到衬底中与空穴结合,从而减小了漏极电流。

2.1.8. 结泄露

反向偏置的 p-n 结有一些漏电。

其中 Is 取决于

- 掺杂水平和

- 扩散区域的面积和周长

- 通常 < 1 fA/μm2

2.1.8.1. 隧穿

通常栅极的漏电是源自于隧穿。载流子可能会隧道穿过非常薄的栅极氧化物,导致栅极漏电流流入栅极。

大隧道电流不仅影响动态节点,还影响静态功耗,因此可能将氧化物厚度 tox 限制为不小于约 8Å。理想 pn 结电流计算式

指向原始笔记的链接

为施加在结上的电压; 为热电压(300K 下为 26mV); 为二极管的反向饱和电流。

由于栅极氧化物已缩小到几个原子层的厚度,因此高 Cox 对于良好的晶体管非常重要。需要使用具有更高介电常数的替代栅极绝缘体。主要挑战:寻找与硅形成高质量界面的材料 – Si3N4(介电常数为 7.8)。其他高 k 材料包括 TiO 和 Ta2O5。

隧道技术的应用,可专门用于创建电可擦除存储设备。 nMOS 的隧道电流比具有 SiO2 栅极电介质的 pMOS 晶体管高一个数量级,因为电子从导带隧道,而空穴从价带隧道并看到更高的势垒不同的电介质可能具有不同的隧道特性。

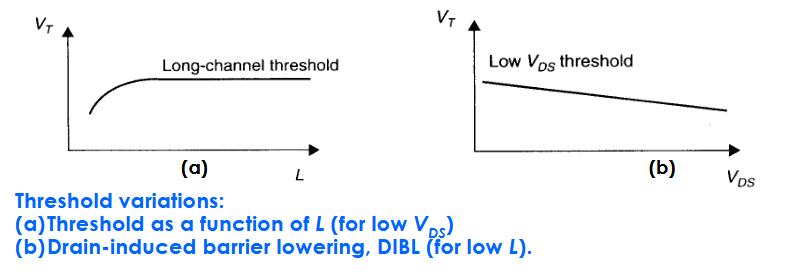

2.1.9. 阈值变化

阈值电压 VT 表明它只是制造技术和施加的体偏置 VSB 的函数。对于设计中的所有 NMOS (PMOS) 晶体管,VT 也假设为常数。随着器件尺寸的减小,该模型变得不准确,阈值电势成为 L、W 和 VDS 的函数。阈值变化在 VT0 的推导中,栅极下方的所有耗尽电荷都被认为源自 MOS 场效应。源极和反向偏置漏极结的耗尽区因此被忽略。然而,在缩小沟道长度的情况下,它们变得相对更加重要。

随着沟道长度

随着沟道长度

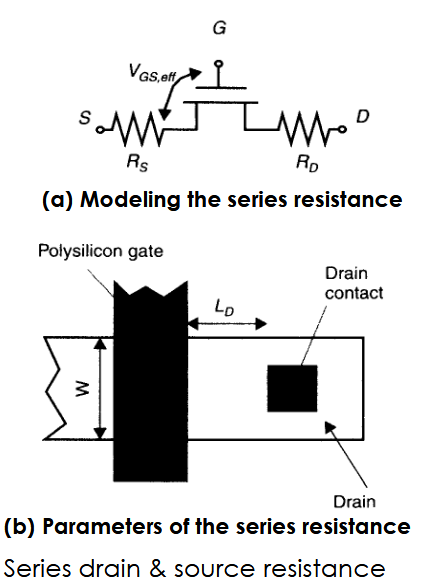

2.1.10. 寄生电阻(源极-漏极电阻)

随着晶体管尺寸的缩小,更浅的结和更小的接触开口是不可避免的。这导致与漏极以及源极区域串联的寄生电阻增加。漏(源)区电阻可表示为,

随着晶体管尺寸的缩小,更浅的结和更小的接触开口是不可避免的。这导致与漏极以及源极区域串联的寄生电阻增加。漏(源)区电阻可表示为,

串联电阻会导致器件性能恶化,因为对于给定的控制电压,ID 会减小。因此,一个重要的设计目标是保持其值尽可能小(对于设备和电路工程师来说)。

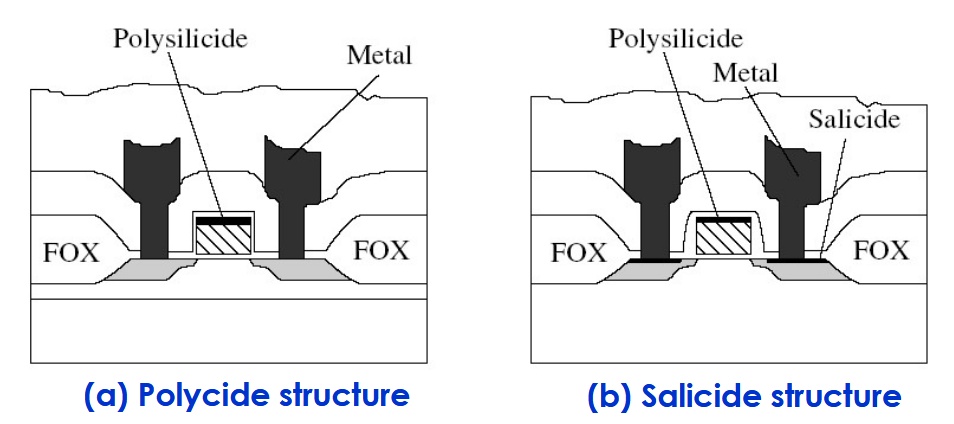

2.1.10.1. 硅化作用(silicidation)

一种替代方案是用低电阻率材料(例如钛或钨)屏蔽漏极和源极区域。沉积的金属与硅发生反应,形成金属硅化物(硅化作用),这将有效地将方块电阻降低至 1 – 4 Ω/sq。硅化也用于降低多晶硅栅极的电阻。从方程可以明显看出。 (2.38)使晶体管比需要的更宽是另一种可能性。 *注:方形材料的电阻是恒定的,与其尺寸无关。

用于通过在多晶硅顶部放置低电阻硅化物(如 TiSi2、WSi2、TaSi2 等)来降低互连电阻率 Salicide 技术(自对准硅化物)提供低电阻源极/漏极连接以及低电阻多晶硅。

用于通过在多晶硅顶部放置低电阻硅化物(如 TiSi2、WSi2、TaSi2 等)来降低互连电阻率 Salicide 技术(自对准硅化物)提供低电阻源极/漏极连接以及低电阻多晶硅。

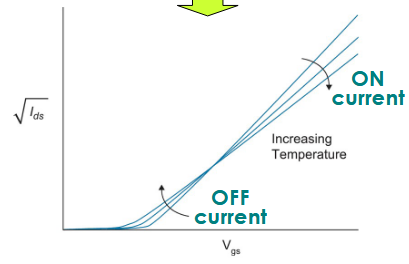

2.1.11. 温度敏感

迁移率和阈值电压都随着温度升高而降低。开启电流随着温度上升减小,关闭电流则是随着上升。因此,电路性能通常在高温下最差——负温度系数。

通过冷却可以提高电路性能:

通过冷却可以提高电路性能:

- 亚阈值泄漏与温度呈指数关系。在低温下工作允许使用较低的 Vt。

- 然后,在较高磁场下会发生速度饱和,以提供更多电流。

- 移动性得到改善,并且在较低的电源下实现改善,这有助于节省电力。

- 耗尽区变得更宽,导致结电容更小。、

- 大多数磨损机制都与温度有关,因此晶体管更加可靠。

问题:

- 低温下,晶体管在较低电压下会击穿。温度依赖性测试可以使用冷冻喷雾和热风枪进行。

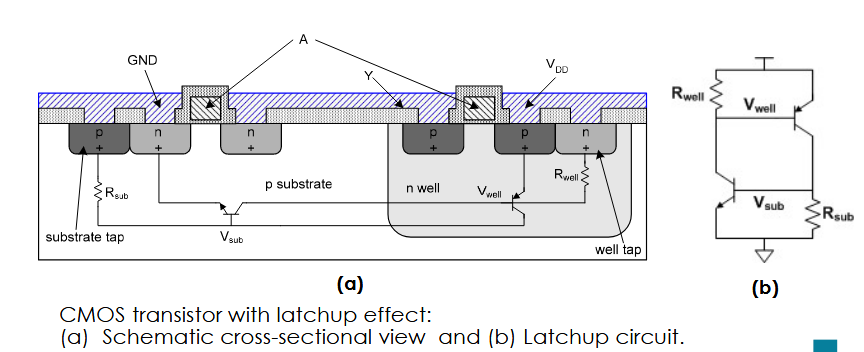

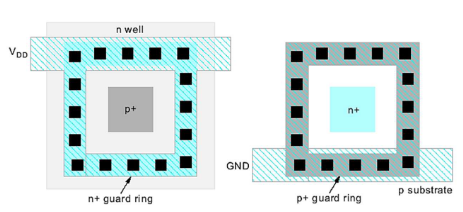

2.2. CMOS 闩锁效应

CMOS 技术包含许多固有的双极晶体管。这些在 CMOS 工艺中尤其麻烦,其中阱和基底的组合导致寄生 n-p-n-p 结构的形成。

触发这些类似晶闸管的器件会导致 VDD 和 VSS 线路短路,从而导致芯片损坏,或者充其量是只能通过断电来解决的系统故障。考虑到 n 阱结构,n-p-n-p 结构由:NMOS 源极、p 衬底、n 阱和 PMOS 源极形成。 • 当两个 BJT 之一正向偏置时(例如,由于电流流过阱或衬底),它会向另一个晶体管的基极供电。该正 FB 会增加电流,直至电路出现故障或烧毁。 • 因此,应通过提供靠近 NMOS/PMOS 器件源极连接的大量阱和衬底接触来最小化电阻 Rnwell 和 Rpsubs。 • 承载大量电流的设备(例如 I/O 驱动器中的晶体管)应被保护环包围。这些圆形阱/衬底触点位于晶体管周围,可进一步降低电阻并降低寄生 BJT 的增益

触发这些类似晶闸管的器件会导致 VDD 和 VSS 线路短路,从而导致芯片损坏,或者充其量是只能通过断电来解决的系统故障。考虑到 n 阱结构,n-p-n-p 结构由:NMOS 源极、p 衬底、n 阱和 PMOS 源极形成。 • 当两个 BJT 之一正向偏置时(例如,由于电流流过阱或衬底),它会向另一个晶体管的基极供电。该正 FB 会增加电流,直至电路出现故障或烧毁。 • 因此,应通过提供靠近 NMOS/PMOS 器件源极连接的大量阱和衬底接触来最小化电阻 Rnwell 和 Rpsubs。 • 承载大量电流的设备(例如 I/O 驱动器中的晶体管)应被保护环包围。这些圆形阱/衬底触点位于晶体管周围,可进一步降低电阻并降低寄生 BJT 的增益

当扩散到衬底的二极管可能变得正向偏置时,闩锁风险最大。 用保护环包围敏感区域以收集注入的电荷。

当扩散到衬底的二极管可能变得正向偏置时,闩锁风险最大。 用保护环包围敏感区域以收集注入的电荷。

2.3. 工艺变化

设备参数在运行之间甚至在同一芯片上都会有所不同!

- 工艺参数的变化,例如杂质浓度密度、氧化物厚度和扩散深度。这些是由沉积和/或杂质扩散过程中的不均匀条件引起的。这会导致薄层电阻和晶体管参数(例如阈值电压)发生变化。

- 器件尺寸的变化,主要是由于光刻工艺的分辨率有限造成的。这会导致 MOS 晶体管的 W/L 变化以及双极器件发射极区域的不匹配。

2.4. 几何依赖性

布局设计者以宽度和长度 Wdrawn 和 Ldrawn 绘制晶体管。 实际门尺寸可能被 XW 和 XL 改变。例如,制造商可以使用更窄的多晶硅创建掩模,或者可以过度蚀刻多晶硅以提供更短的通道(负 XL),而不改变整体设计规则或金属间距。 源极和漏极也倾向于通过 LD 在栅极下方横向扩散,从而产生载流子必须在源极和漏极之间横穿的更短的有效沟道长度。 类似地,WD 引起的体扩散会减小有效沟道宽度。 因此,有效晶体管长度和宽度为几何依赖性

指向原始笔记的链接

3. I-V 关系——线性区和饱和区

3.1. 线性区

当满足

沟道电荷计算式

指向原始笔记的链接

长沟道 MOS 器件线性区漏极电流计算式

指向原始笔记的链接

为工艺跨导参数

器件增益系数计算式

指向原始笔记的链接

为工艺跨导系数; 为沟道的厚度; 为沟道的长度

3.2. 饱和区

沟道长度调制效应

当

的时候,沟道的长度 因为漏极和衬底之间的耗尽区的扩展而逐渐缩小为 。引入沟道长度调制系数来表征。这个效应会导致晶体管的饱和电流 随 缓慢线性增加,从而导致了高输出电导。

沟道长度调制效应耗尽层增量计算式

指向原始笔记的链接 指向原始笔记的链接沟道长度调制系数

为了代表漏源电压对于漏极电流的调制而引入的一个较小的经验系数

指向原始笔记的链接,这个系数就是沟道长度调制系数。这个系数的加入使得沟道长度调制效应得以用物理公式来解释。

NMOS 饱和区的漏极电流计算式

指向原始笔记的链接

为沟道长度调制系数。

4. MOS 晶体管理论

Transclude of MOSFET

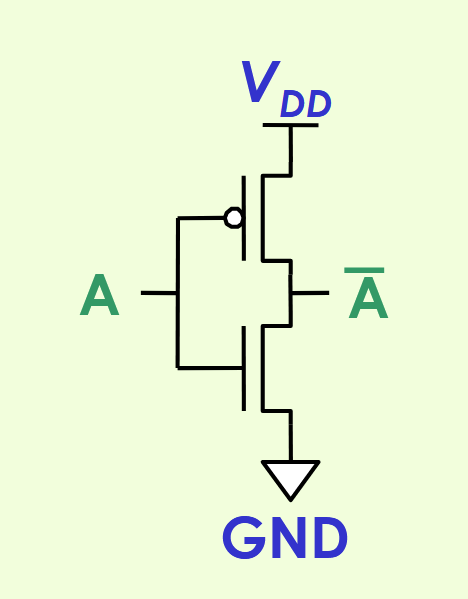

前面我们讲过 MOS 的简单开关模型,于是我们可以利用 NMOS 和 PMOS 对于高低电平的不同响应来构建电路,其中,最简单的就是一个 CMOS 反相器。

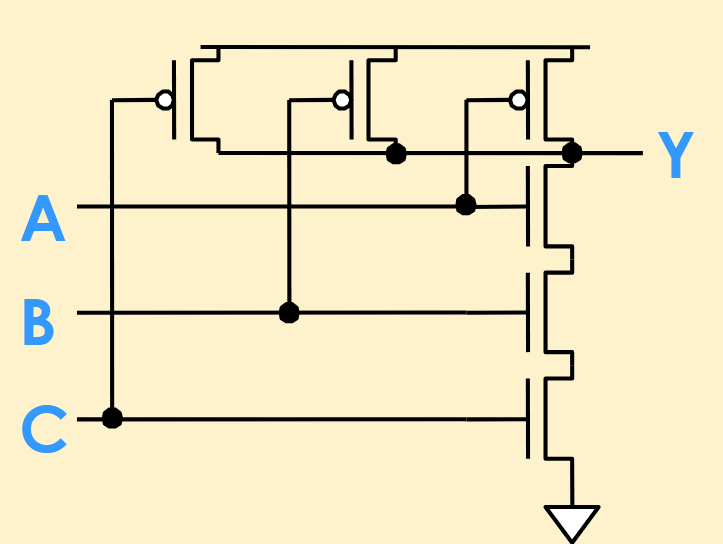

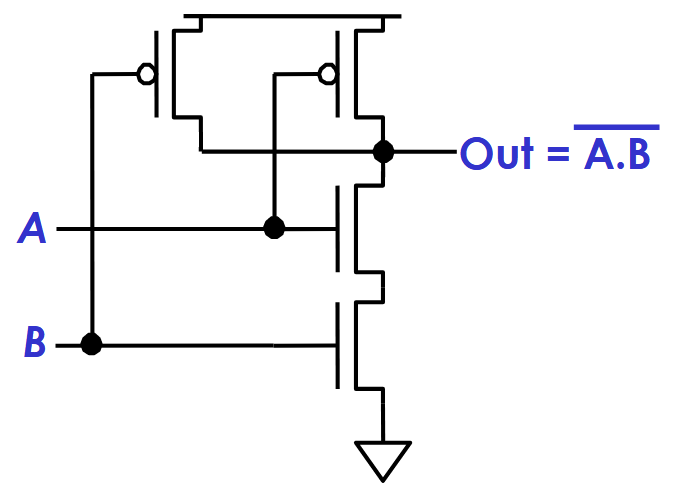

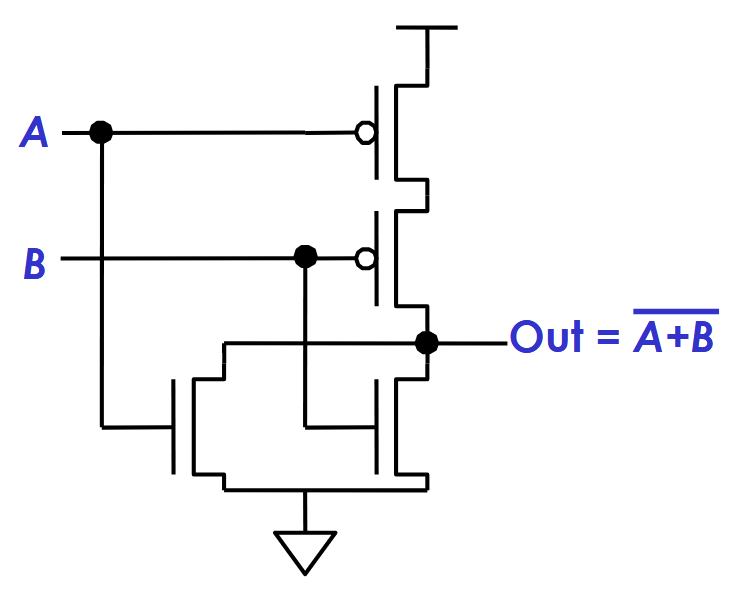

5. CMOS 器件

CMOS 器件电路很好记。CMOS 器件的电路分为 PUN 和 PDN,即上拉网络和下拉网络。先将逻辑式取反,然后画出对应的 PDN 的 NMOS 电路,再画出对偶的 PUN 的 PMOS 电路即可。

5.1. CMOS 反相器

将 NMOS 和 PMOS 串联,且 PMOS 接

5.2. CMOS NAND 门

与非门结构如上,只有在 A 和 B 同时为高电平的时候,才输出低电平。

5.3. CMOS NOR 门

或非门结构如上,只有 A 和 B 同时为低电平的时候,输出才为高电平。

5.4. 输入与非门