1. 基础知识复习

关于 MOSFET 的简单看 《Chapter 2 硅 MOSFET 》笔记复习。

关于反相器的看看第 5 章 CMOS 反相器 笔记

2. 存储器

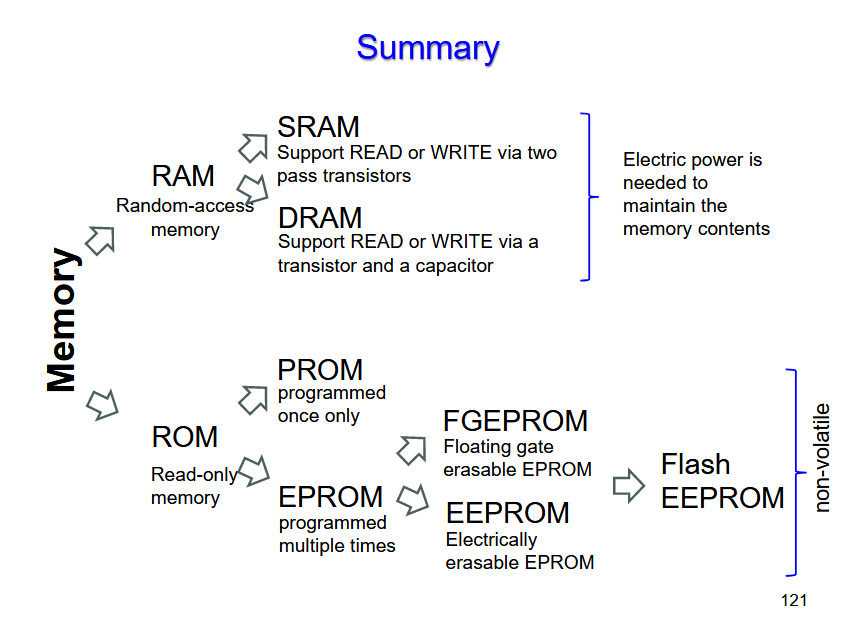

半导体存储器分为挥发性(volatile)以及非挥发性(non-volatile)存储器两种。分别的代表就是 RAM(random access memory) 为主的挥发性存储和 ROM(read-only memory) 为主的非挥发性存储器。

2.1. RAM

RAM 又能分类为 SRAM 和 DRAM。SRAM 只要通电就能够存储信息,并且在读取周期内不会丢失数据。而 DRAM 使用电容器临时存储数据,必须定期刷新以防止信息丢失。

2.1.1. 基本存储阵列的结构

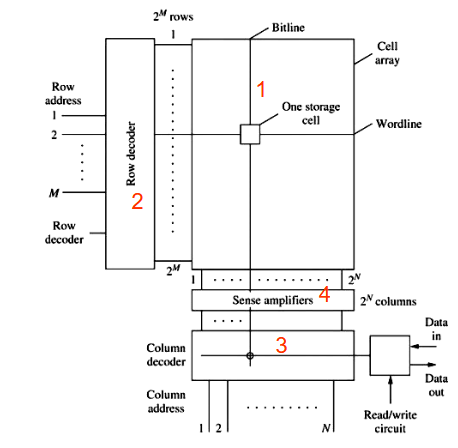

一个典型的存储器结构如上,主要有四个部分,

一个典型的存储器结构如上,主要有四个部分,

- 存储阵列,由

个存储单元构成的阵列; - 行解码器(地址解码器),也叫字线,用于控制对那些行的存储器进行操作,输入 M 位,用于控制

行; - 列解码器(数据解码器),也叫位线,用于对字线控制可操作的行进行读写,输入 N 位,用于控制

个列; - 检测放大器,它们连接到位线,它们需要检测存储单元的状态并将信号恢复到完整的逻辑电平。

2.2. SRAM 单元

2.2.1. 2反相器锁存

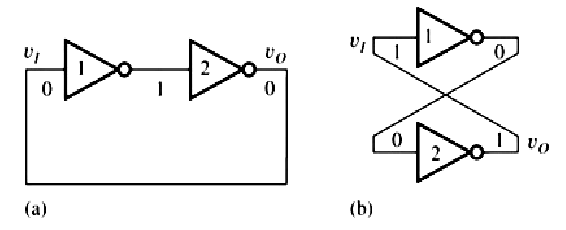

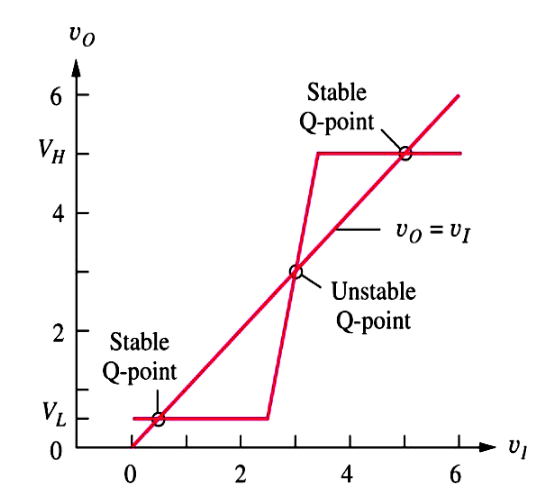

2 反相器锁存将两个反向器首位相接,使得每个反相器的输入和输出都是某个固定的状态。锁存器通常只有两种称为双稳态的稳定状态。但是,它有可能进入

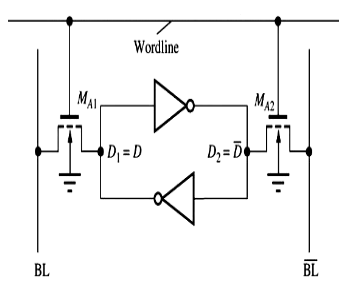

2.2.2. 六晶体管 (Six-T) 单元

6-T 单元在锁存器的基础上,加上了

6-T 单元在锁存器的基础上,加上了

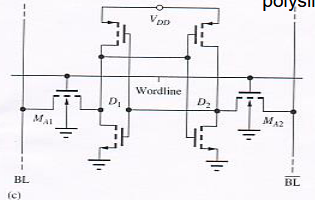

2.2.2.1. 常用的 SRAM 存储单元

-Six-T-NMOS-memory-cell..png)

两个耗尽型 NMOS 和四个增强型 NMOS 构成;

![]() 有多晶硅负载电阻的NMOS 存储单元。

有多晶硅负载电阻的NMOS 存储单元。

6-T CMOS 存储单元(主要使用)。

CMOS 存储单元与其他存储单元相比的优点:

6-T CMOS 存储单元(主要使用)。

CMOS 存储单元与其他存储单元相比的优点:

- 功耗小

- 体积小

- 漏电流小

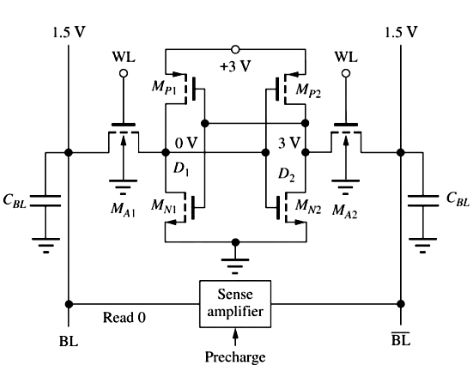

2.2.2.2. 6-T 单元的读 0 操作

假设有

假设有

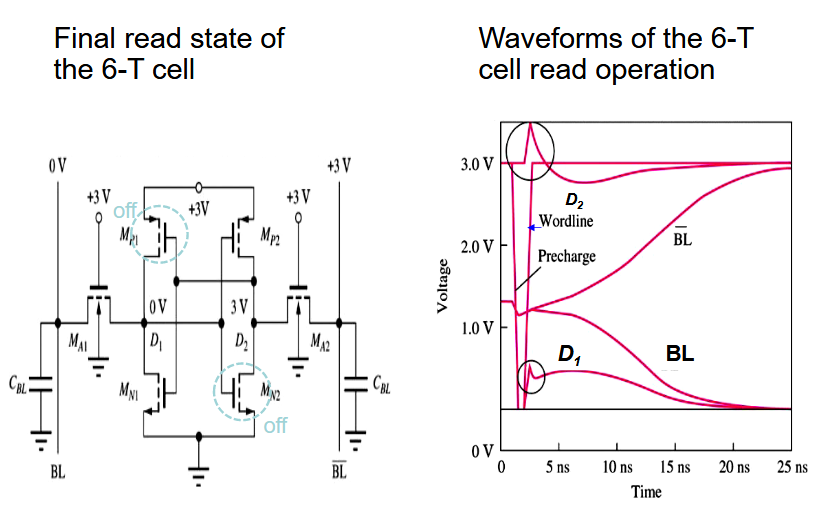

由于电流 i1 和 i2 造成的 D1 和 D2 节点电压的任何干扰都可以通过锁存操作快速校正,并且存储在单元中的原始数据得以保留。可以看下面的波形图进行理解,这也是为什么位线要预充电到

2.2.2.3. 6-T 单元的读 1 操作

读“1”操作遵循与之前相同的概念,只是交换了存取晶体管的源极和漏极(电位较低的端子为源极)。请注意,此特定单元有大约 20 ns 的延迟。

2.2.2.4. 例题

Calculate

Solution

一点复习,免得忘了:

注意这里的单位取决于工艺跨导参数的单位(

2.3. DRAM 单元

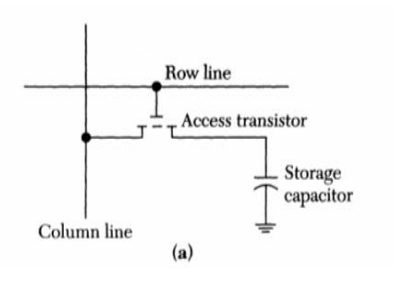

前面讨论的 SRAM 单元包含一个锁存电路,可通过两个传输晶体管访问该锁存电路以进行读或写操作。DRAM 单元基于电容器上存储的电荷进行操作。最简单的 DRAM 单元由一个 MOS 晶体管和一个电容器组成。

2.3.1. 单晶体管(1-T)DRAM 单元

1-T 单元由 Robert H. Dennard 于 1970 年在 IBM Thomas J. Watson 研究中心发明。它由一个存取(传输)晶体管和一个存储电容器组成。

1-T 单元由 Robert H. Dennard 于 1970 年在 IBM Thomas J. Watson 研究中心发明。它由一个存取(传输)晶体管和一个存储电容器组成。

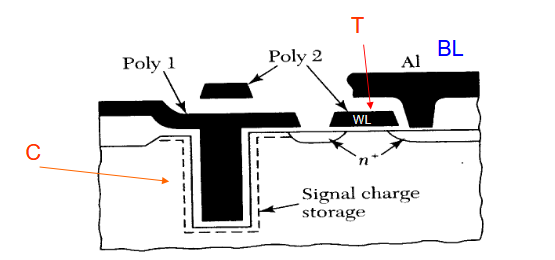

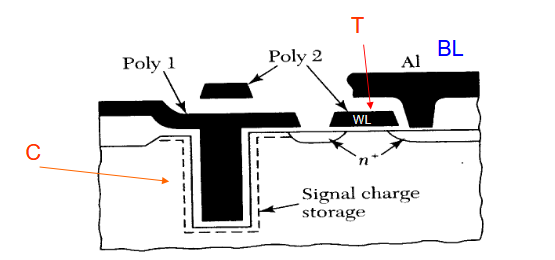

位线是 n+ 掺杂的,字线则是金属线用于减小寄生电阻和电容。

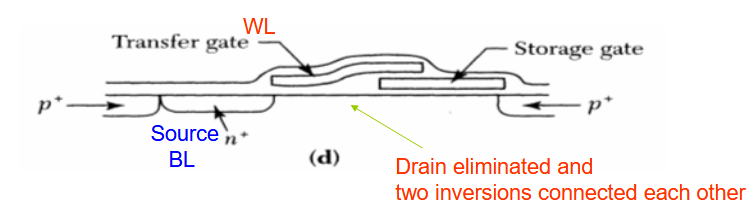

MOSFET 的内部漏极区域充当存储栅极下方的反型层与存取晶体管之间的导电连接。存储电容器使用沟道区作为一块板,多晶硅栅极作为另一块板。

漏极区可以通过使用双层多晶硅方法来消除。因此,通过晶体管和存储栅极下方的反型层的连续性,可以将来自位线的电荷直接传输至存储栅极下方的区域。

为了满足高密度的要求,DRAM 结构已经扩展到具有堆叠或沟槽电容器的三维。下图显示了一个简单的沟槽单元结构。

可以通过增加沟槽的深度来增加电池的电容,而不增加电池所占据的硅的表面积。

可以通过增加沟槽的深度来增加电池的电容,而不增加电池所占据的硅的表面积。

2.3.2. 写数据

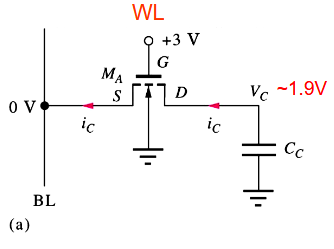

2.3.2.1. 存 “0”

- 将位线设为 0V

- 将字线设为 3V

如果 C 原本就是 0V,则无变化。如果原本是存储了“1”,则会形成电流。

假设

假设

2.3.2.2. 存“1”

- 将位线设为 3V

- 将字线设为 3V

如果原本是“1”则无变化,如果原本是“0”,则有流向电容的电流。

阈值电压计算式

指向原始笔记的链接

为零偏置阈值电压; 为体效应系数; 为阈值表面电压; 为源衬电势差。

长沟道 MOS 器件线性区漏极电流计算式

指向原始笔记的链接

为工艺跨导参数

(这里不考虑沟道长度调制系数)NMOS 饱和区的漏极电流计算式

指向原始笔记的链接

为沟道长度调制系数。

2.3.3. 读数据

2022 #EE6604期末/2023

- 位线预充电至大约 VDD/2 或 VC/2。

- 通过将 WL 升高至 3V (VDD) 打开 MA

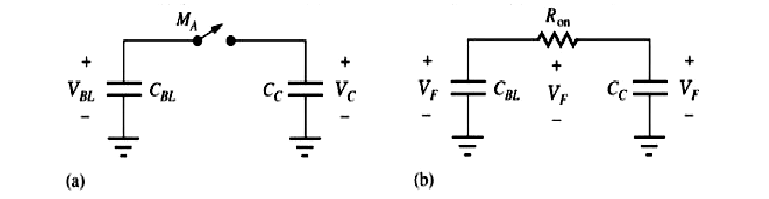

2.3.3.1. 电荷共享模型

(a) 访问晶体管激活之前的电路模型 (b) 访问开关闭合之后的电路。

MA 开启前的初始总电量,

MA 开启前的初始总电量,

MA 开启并稳定之后,

假设没有电荷损失,

要检测的信号是位线相对于其初始预充电值的变化:

如果假设

这意味着 VBL 和 VF 这两个电压之间的差异非常小,但仍然可以被读出放大器测量,从而可以识别存储的逻辑电平。

2.3.3.2. 充电时间常数

除了理想开关的情况外,电荷转移不可能瞬时发生。电路中的电压和电流将随时间常数

充电时间常数计算式

指向原始笔记的链接

为存取晶体管的导通电阻; 为位线电容; 为存储电容的电容值,有

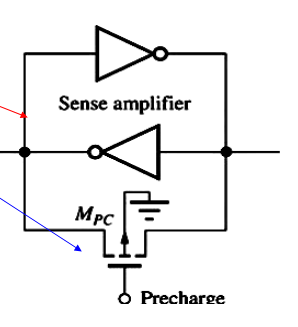

2.4. 读出放大器 sense amplifier

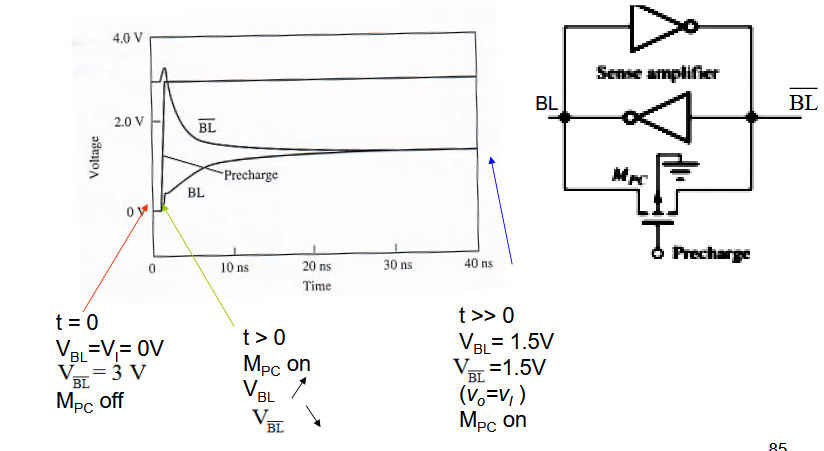

读出放大器由两个反相器锁存器和一个额外的预充电晶体管组成。

锁存器的功能:

锁存器的功能:

- 检测流经存取晶体管的小电流或电荷共享期间出现的小电压差

- 快速将信号放大到完整的片内逻辑电平

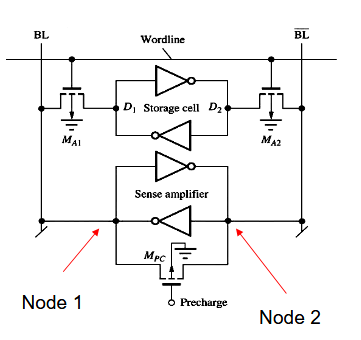

2.4.1. 用于 6-T 单元的读出放大器

和 6-T 单元并联。

和 6-T 单元并联。

预充电 T (MPC) 在打开时将提供低电阻连接。强制读出放大器的两个节点保持相等的电压并强制锁存器在不稳定平衡下运行,由此  达到 vo= vI 所需的时间受到以下限制:

达到 vo= vI 所需的时间受到以下限制:

- 预充电 T 的 W/L

- CBL

- 锁存器中反相器的 W/L。

一旦达到平衡(vo=vI),预充电晶体管就可以关闭。并且可以激活 WL 来读取单元格。

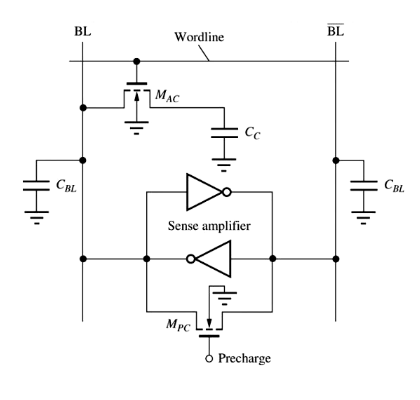

2.4.2. 用于 1-T 单元的读出放大器

6-T 单元中使用的读出放大器可以以相同的方式用于 1T 单元。但预充电后需要较长时间才能达到稳定状态。

6-T 单元中使用的读出放大器可以以相同的方式用于 1T 单元。但预充电后需要较长时间才能达到稳定状态。

2.4.2.1. 1-T 单元的放电率

放电率(discharge rate)的定义为,

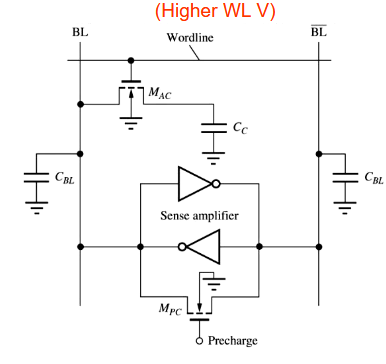

2.5. 升压字线电路

高速度意味着快速访问,需要高放电倍率。高放电倍率需要高充放电电流。这可以通过采用被称为升压字线的高字线电压来实现。

高速度意味着快速访问,需要高放电倍率。高放电倍率需要高充放电电流。这可以通过采用被称为升压字线的高字线电压来实现。

2.6. ROM

ROM 永久存储数据,能够随机访问并且是非易失性的(断电时它们不会丢失存储内容)。它们最初是预编程的,并且编程的数据是只读的。不过,也有可擦除 ROM,如果需要的话可以重新编程。

2.6.1. 应用

由于 ROM 的低功耗和非易失性,广泛应用于便携式电子系统,例如:蜂窝电话、数码相机和智能 IC 卡。其他包括用于家庭视频游戏的卡带和用于科学计算器的插件模块。

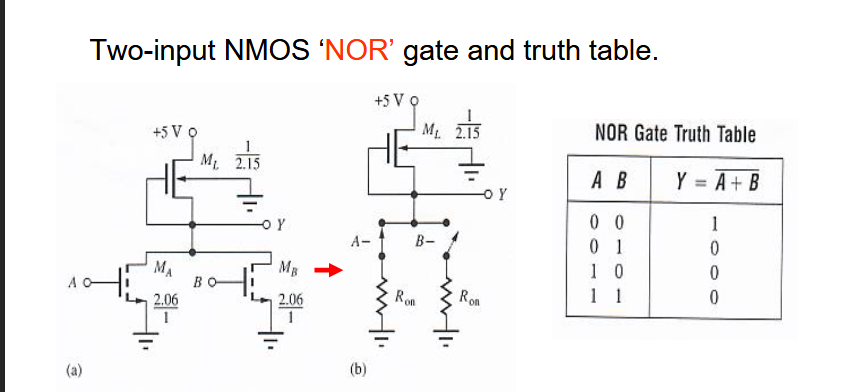

2.6.2. ROM 阵列

ROM 阵列可以基于“或非”门或“与非”门。

2.6.3. 掩模ROM

掩模(或掩模)ROM 必须在 IC 设计和后续制造过程中完成。因此,如果出现设计错误,则必须重新设计和重新制造 IC。ROM 被组织为 2N 个字的数组。每个字包含一些位,例如 4、8、12、16、18、24、32、48、64,具体取决于应用。

2.6.4. 熔断链路 PROM

可编程 ROM (PROM) 可用,可在用户端编程以根据需要存储数据。但是,一旦用户编程,存储的数据就无法更改(只能编程一次)。

最初,每个存储单元都有一个通过熔丝连接的晶体管,使其输出保持为“0”。通过向各自的保险丝发送高电流,可以将任何单元上的“0”更改为“1”,以将其永久断开。保险丝烧断后,电池输出无法恢复至 0。W1 (1011)、W2 (1101)

2.6.5. EPROMs

有可多次编程的可擦除可编程只读存储器 (EPROM) 单元。这种 EPROM 单元仅包含一个存储晶体管,该晶体管通常保存多余的电荷。要重新编程 ROM,必须擦除旧数据。这可以通过从正在使用的系统中取出芯片并将其置于特殊的紫外线源下进行擦除来完成。

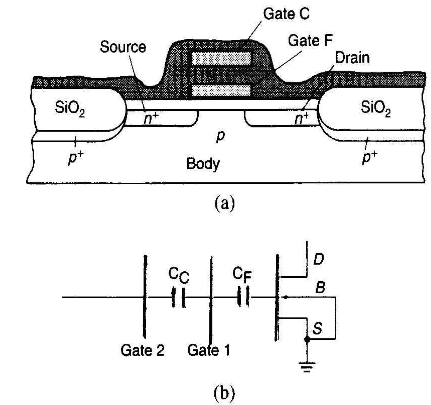

浮栅 EPROM 单元

(a) 基本叠栅 EPROM 晶体管。(b) 具有等效控制电容和浮栅电容的电路符号。

(a) 基本叠栅 EPROM 晶体管。(b) 具有等效控制电容和浮栅电容的电路符号。

- 栅极 C - 控制栅极

- 栅极 F - 浮栅

- CC - 控制栅极电容

- CF – 浮栅电容。

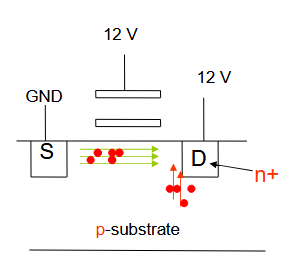

如何编程?假设 EPROM 单元的浮动栅极最初没有电荷。要写入“0”,无需执行任何操作。要写入“1”,EPROM 单元的控制栅极和漏极需要升高到高电压(通常为 12 V)并持续几百微秒,而源极和衬底处于 0 V。

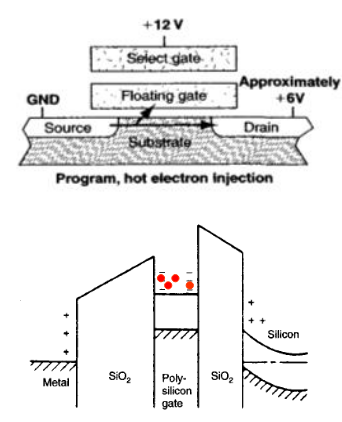

2.6.5.1. 机制

大的漏极电流在其正常传导模式(电子流

大的漏极电流在其正常传导模式(电子流

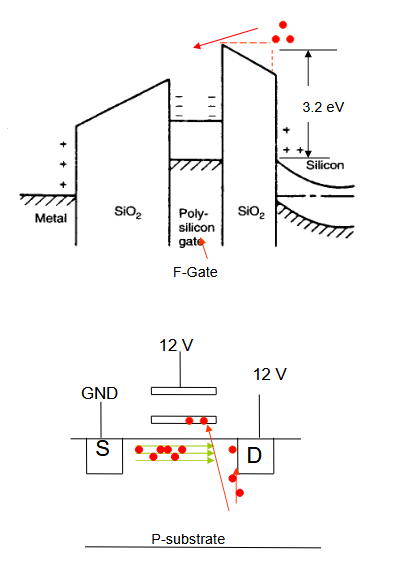

一旦热电子获得足够的能量,它们就可以克服衬底和氧化物绝缘体之间存在的 3.2 eV 能垒(红虚线)。(不会发生隧道效应)穿过薄氧化物的一小部分电子被捕获在浮栅上。由于带负电的电子被捕获,氧化物的能带随后变成固体能带。

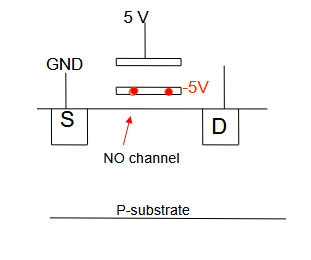

假设被捕获的电子会产生大约 –5V 的电位,当 5V 的信号施加到控制栅极时,晶体管中不会形成沟道,这表示单元中存储的是逻辑“1”。

假设被捕获的电子会产生大约 –5V 的电位,当 5V 的信号施加到控制栅极时,晶体管中不会形成沟道,这表示单元中存储的是逻辑“1”。

2.6.5.2. 如何擦除

将 EPORM 单元(晶体管)暴露在紫外线辐射下约 20 分钟,即可去除存储在浮栅中的电荷。机理,在紫外光(发射 2537 Å (4.9 eV) 辐射的汞弧灯或蒸气灯)下,入射光子被浮动多晶硅栅极的导带和价带中的电子吸收。从进入氧化物的多晶硅栅极激发的电子被局部场扫至控制栅极或衬底。问题:需要将芯片从使用中的系统中移除,并且所有单元都将被擦除。

2.6.6. 电可擦除 PROM (EEPROM)

EEPROM 技术 金属-氮化物-氧化物-硅 (MNOS) 技术(20 世纪 70 年代初期)。 • 硅-氧化物-氮化物-氧化物-半导体 (SONOS) 技术(20 世纪 70 年代初)。

浮栅隧道氧化物 (FLOTOX) 技术。 相似点和不同点它们都利用了称为 Fowler-Nordheim 隧道效应的效应(使用强场诱导低能电子隧道穿过约 10 nm 的薄氧化物)。 FLOTOX 存储器捕获穿过导电(浮动)栅极中的薄氧化物的电子,而 MNOS 和 SONOS 存储器将隧道电子捕获在绝缘氮化物内。

2.6.6.1. FLOTOX 技术

2.6.7. 闪存

闪存是可以通过使用电擦除信号同时擦除所有存储单元的内容的设备。

大多数闪存均采用 EPROM 的热电子注入技术进行编程,并通过从浮栅到漏极区域的 Fowler-Nordheim 隧道进行擦除。采用 EEPROM 技术的当前一代闪存仅需要 5 V 电源。该技术适用于不仅需要比 EEPROM 更多存储容量,而且还需要比 EPROM 更快、更频繁编程的应用。

2.6.7.1. 编程

热电子注入技术。S-D 电压 (6V) 产生扫过通道的热电子。选定(控制)栅极上的高电压(12 V)克服了氧化物势垒并吸引电子穿过薄氧化物层。

2.6.7.2. 擦除

福勒-诺德海姆隧穿。

漏极保持浮动,选择栅极接地,源极电压为 12 V。 S 电压在浮动栅极和源极之间的薄氧化物上产生高场,从而拉出电子。

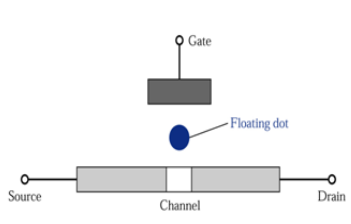

2.6.8. 单电子存储单元

通过将浮栅的长度减小到超小尺寸,例如 10 nm,可以获得单电子存储单元(SEMC)。由于尺寸小,电容也非常小(1 aF、1 atto F = 10−18 F)。SEMC 是一种终极浮栅存储单元,因为它只需要一个电子来存储信息。

通过将浮栅的长度减小到超小尺寸,例如 10 nm,可以获得单电子存储单元(SEMC)。由于尺寸小,电容也非常小(1 aF、1 atto F = 10−18 F)。SEMC 是一种终极浮栅存储单元,因为它只需要一个电子来存储信息。

2.7. 总结