Q1 描述三种 ESD 模型(即 HBM、MM 和 CDM)并绘制它们的典型电流波形

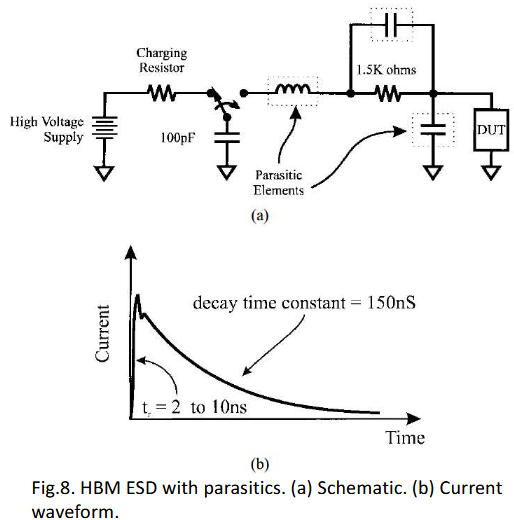

HBM:HBM 是人体在充电之后,接触集成电路的引脚,同时 IC 的引脚接地引起的静电释放。其典型电流如下,关键点是 2ns 左右的小电流快速升高,随后 150ns 的电流缓慢降低,且电压约为 4000V。

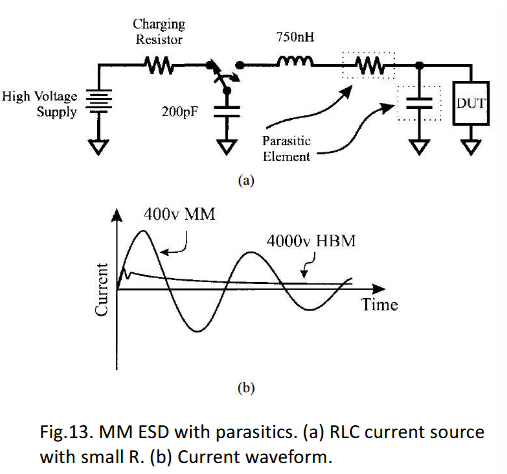

MM:MM 用于描述在 IC 的制造过程中,制造设备逐渐积累电荷,然后接触 IC 器件释放电荷的过程。其电流特征如下,由于电感的存在使得电流呈现振荡的特征,电压为 400V 左右,电流远高于 HBM。

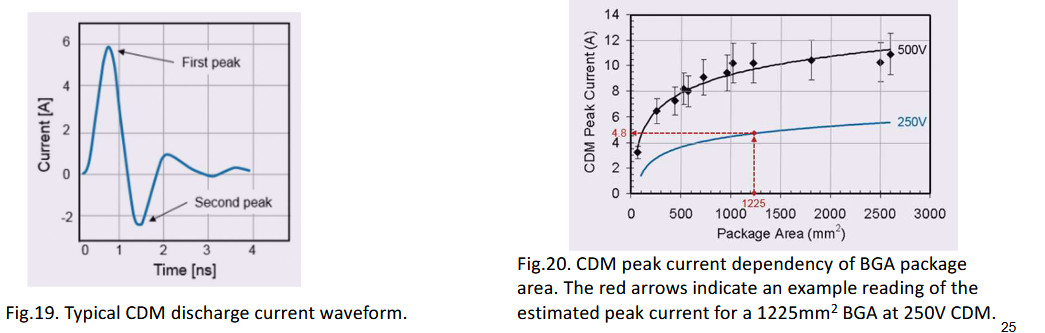

CDM:表示 IC 积累电荷向其他导体释放电荷的过程。其电流特征在于 2ns 内快速出现的两个电流高峰。

Q2 基本上有两种类型的保护设计方式:(1) 本地钳位方法和 (2) 电源轨钳位方法,如图 2 所示。讨论图 2 中所示的各种 ESD 应力模式。

5.3.2.1. ESD 钳位

如图 24 所示,ESD 钳位电路用于应对不同 ESD 应力模式的防护:

ESD 应力模式包括:

- 电源轨 ESD 钳位:电源轨之间的 Vdd 至 Vss(或 Vss 至 Vdd)ESD 应力

- 输入/输出(I/O)与 Vdd/Vss 之间的 ESD 钳位(局部钳位):

- 正极对 Vss(PS)模式

- 负极对 Vss(NS)模式

- 正极对 Vdd(PD)模式

- 负极对 Vdd(ND)模式

ESD 钳位电路必须在 ESD 事件期间提供低阻抗泄放路径,同时在正常电路工作条件下保持关断状态,且静态漏电流尽可能低。

电源轨 ESD 钳位电路是应对不同 ESD 应力模式的关键保护元件,能够通过高效泄放路径在各种 ESD 应力条件下保护内部电路。

指向原始笔记的链接

Q3 列出片上 ESD 保护的总体目标

5.3.2.2. 片上 ESD 保护的总体目标

• 钳制 ESD 电压以分流 ESD 应力电流 • 快速开启(响应时间<300 皮秒) • 承载 1-2 安培或更大电流持续 150 纳秒 • 具备低导通电阻 • 在焊盘区域占用最小面积 • 引入最小寄生电容 • 产生最低串联电阻 • 不受工艺漂移影响 • 可承受多次脉冲冲击 • 提供人体放电模型(HBM)和器件充电模型(CDM)防护 • 不影响芯片功能测试 • 不会增加静态电流(IDDQ)或 I/O 漏电流 • 通过老化测试验证可靠性 • 避免引发闩锁效应或电气过应力(EOS)失效

指向原始笔记的链接

Q4、5、6、7 二极管、GGNMOS、SCR 的 I-V 特性以及重要参数,截面图以及工作机制

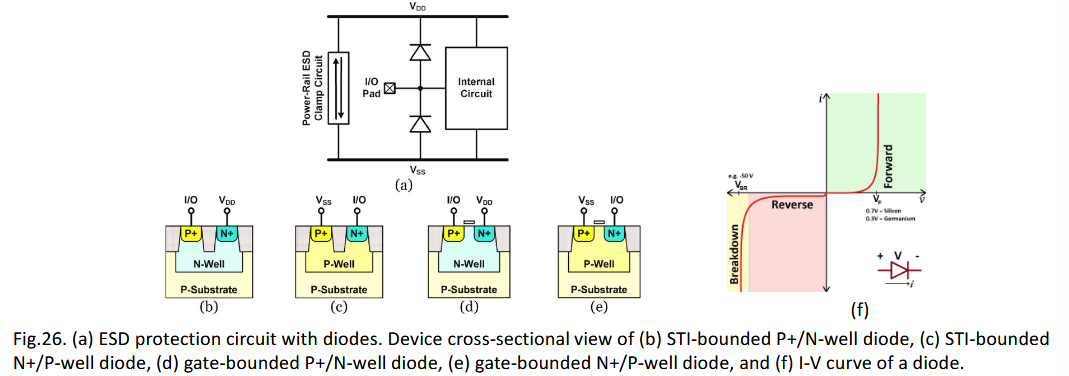

5.3.2.4. 二极管 ESD 保护

二极管是一种典型的 ESD 保护器件,具有单向放电路径。用于高频应用的双二极管 ESD 保护电路如图 26(a) 所示,其中 I/O 焊盘上的两个 ESD 二极管与开启高效的电源轨 ESD 钳位电路配合,在正向偏置条件下放电 ESD 电流 @ > ~ 0.7V。

对于正向的二极管,触发电压和保持电压相同,约为 0.7V。这对于低压 IC 的 ESD 保护设计来说非常好,因为这种应用所需的触发电压相对较低。但是为了保护具有较高工作电压的引脚,需要串联几个二极管(即堆叠配置,见图 27)以增加触发电压(即触发电压是 0.7 V ×二极管数量)大于 ESD 设计窗口的下限。这样做的缺点是占用较大的芯片面积并增加 pin 的寄生电阻。

指向原始笔记的链接

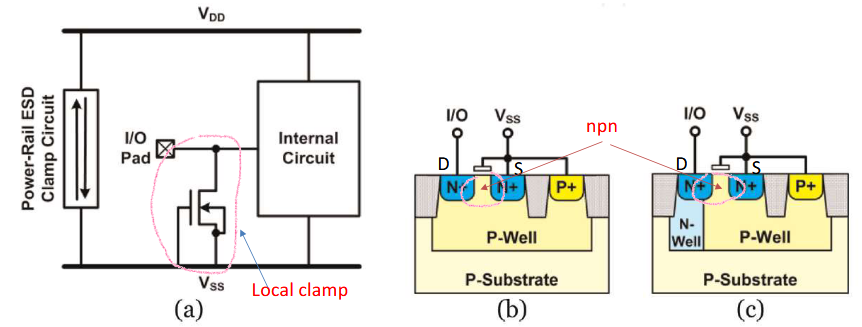

5.3.2.5. GGNMOS ESD 保护

CMOS 技术中常用的 ESD 保护电路是接地栅极 NMOS (GGNMOS),如图 28(a) 所示。在这个 ESD 保护电路中,NMOS 的栅极接地,以便在正常电路工作期间保持关闭。

[! note] 正向 ESD:静电放电导致 I/O 引脚电压高于电源电压

5.3.2.5.1. GGNMOS 工作原理

当 I/O 焊盘(漏极)出现正向 ESD 事件时:

- 寄生 npn 双极型晶体管的集电极-基极结反向偏置至雪崩击穿点(触发点)

- 雪崩击穿产生大电流

从基极流向地端时在寄生电阻 ( ) 上产生压降,形成正向电压 - 当

时,寄生 npn 晶体管导通 - npn 晶体管导通后,I/O 焊盘与地之间形成低导通电阻,此时可观察到回滞现象

图 29 展示 GGNMOS 中寄生 npn 晶体管与衬底电阻 (RSUB) 形成的等效电路; 图 30 显示通过传输线脉冲 (TLP) 系统测量的 GGNMOS 正向 I-V 曲线中的回滞特性;

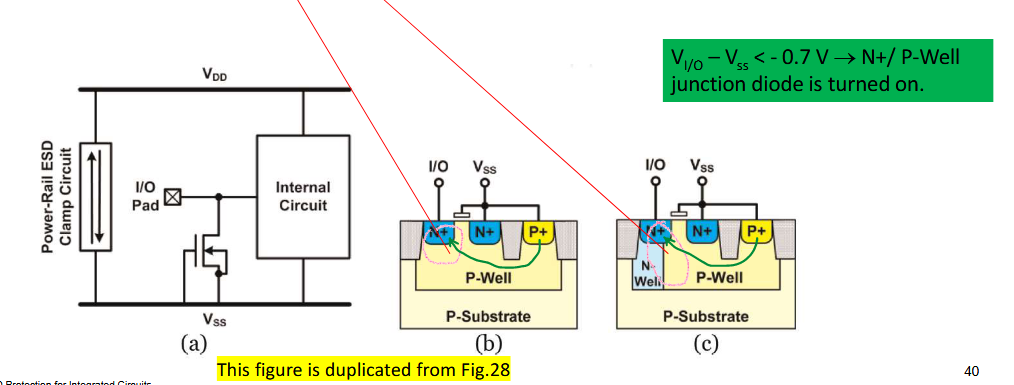

当 I/O 焊盘(漏极)出现负向 ESD 事件时:

- 借助寄生结二极管的作用,当 I/O 电压低于

电压时 GGNMOS 导通 - 结二极管导通后,I/O 焊盘与

之间形成低导通电阻 - 此时电流从 P 阱 (

) 流向 N+(I/O 引脚)

[! note] GGNMOS 的栅极接地,使得 MOS 始终关闭。

- 正向 ESD:基极-集电极雪崩击穿产生电流,电流流经寄生电阻产生电压,使得寄生 npnBJT开启形成低阻通路;

- 反向 ESD:n+扩散区和衬底形成的寄生二极管导通。 都是通过寄生器件起到防护 ESD 的作用。

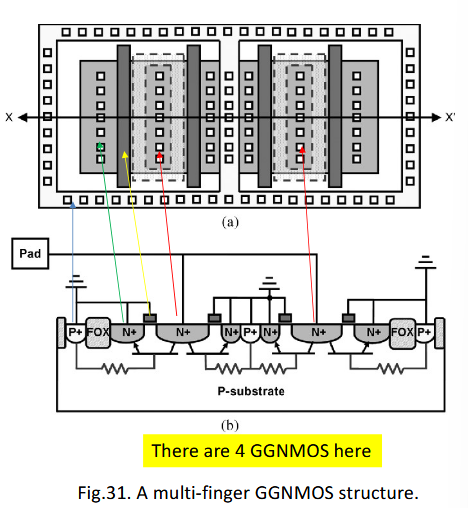

5.3.2.5.2. GGNMOS 结构

GGNMOS 通常采用中心漏极的多指结构绘制, 以节省总布局面积, 如图 31 所示。图 28 (b) 展示了一个单指 GGNMOS 的器件横截面视图。多指结构可以通过将此类单指结构组合实现, 每两个相邻指之间共享漏极和源极区域。对于高频应用, 必须考虑 GGNMOS 的寄生电容。

为提高 GGNMOS 的 ESD 健壮性, 需要更大的结面积, 这会增加 N+/P 阱底部结的电容。因此, 必须在 ESD 健壮性与电容之间找到一个平衡点。减少 N+/P 阱底部电容的一个可行方案是在 N+ 漏极下方使用 N 阱注入, 如图 28 (c) 所示。大部分底部 N+/P 阱电容随后被 N 阱 /P 阱侧壁电容和 N 阱 /P‐ 所取代衬底底部电容。

指向原始笔记的链接

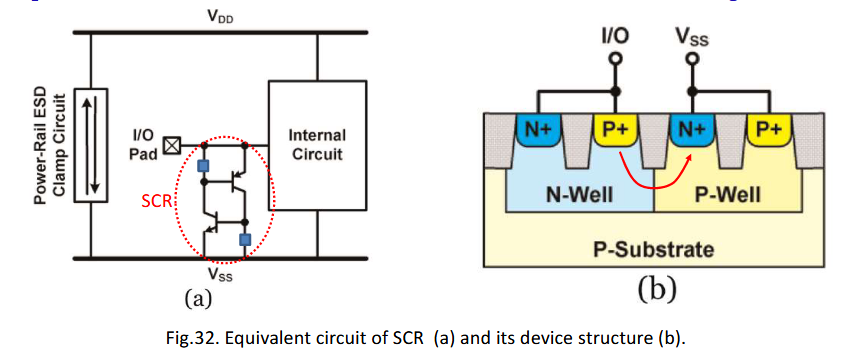

5.3.2.6. SCR ESD 保护

SCR 器件可用于高频电路中的 ESD 保护,因为它在更小的布局区域内具有更高的 ESD 健壮性和更低的寄生电容。 SCR 器件可以安全地使用在低电源电压的先进 CMOS 技术中,而不会有闩锁危险。 SCR 的等效电路及其器件结构如图 32 所示。

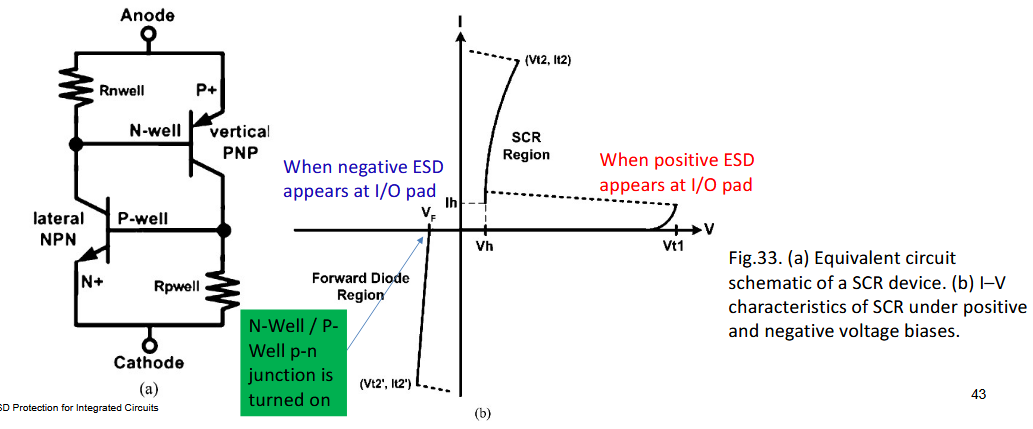

SCR 器件由横向 NPN 和垂直 PNP BJT 组成,形成 CMOS 工艺固有的 2 端子/4 层 PNPN (P+/N-well/P-well/N+) 结构。具有 P 井电阻 (

) 和 N 井电阻 ( ) 的 SCR 的等效电路如图 33(a) 所示。 SCR 器件的 DC I-V 特性如图 33(b) 所示。

SCR 的触发电压主要由 N 阱/P 阱结的雪崩击穿电压决定。在 0.25μm CMOS 工艺中该电压可达 22V,0.13μm 工艺中则为 18V。

当 SCR 阳极施加的正向电压超过击穿电压且阴极接地时,雪崩击穿机制将产生空穴和电子电流。空穴电流通过 P 阱流向接地的 P+扩散区,电子电流则通过 N 阱流向 SCR 阳极连接的 N+扩散区。

当 Rpwell(Rnwell)两端压差超过 0.7V 时,NPN(PNP)双极晶体管导通,从而触发 SCR 闩锁动作。最终 SCR 将成功进入闩锁状态。一旦 SCR 被触发,维持 NPN 和 PNP 导通所需的保持电流可通过闩锁的正反馈机制产生,无需再次依赖雪崩击穿。因此在体 CMOS 工艺中,SCR 通常具有约 1.5V 的较低维持电压(参见图 33 (b) 触发点与维持点)。

若 SCR 阳极施加负电压,其固有寄生二极管(N 阱/P 阱结)将正向偏置,将负电压钳位在约 1V 的较低电平(二极管导通电压)。图 33 (b) 展示了正向偏置下 N 阱/P 阱结的 I-V 特性。无论 ESD 能量极性为正或负,SCR 器件均能将过应力电压钳位至较低电平,因此在 CMOS 集成电路中能以较小版图面积实现最高的 ESD 健壮性。

指向原始笔记的链接

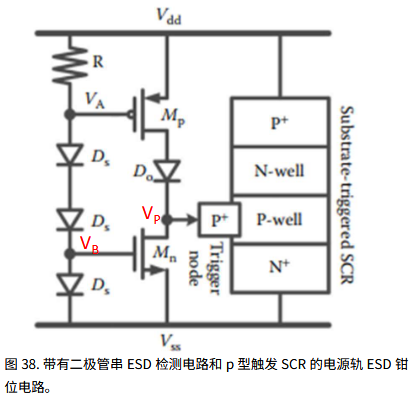

Q8 绘制带有二极管串 ESD 检测电路和 p 型触发 SCR 的电源轨 ESD 箝位电路。解释电源轨 ESD 箝位电路的工作原理。

5.3.2.9. 电源轨 ESD 钳位电路:二极管串 ESD 检测 + SCR 钳位

图 38 展示了电源轨 ESD 钳位电路, 该电路由二极管串 ESD 检测电路和作为主要 ESD 钳位器件的 p 型触发 SCR 构成。该设计采用二极管串和电阻来实现对 ESD 事件的检测通过高压电平而非快速上升时间。

正常操作 :

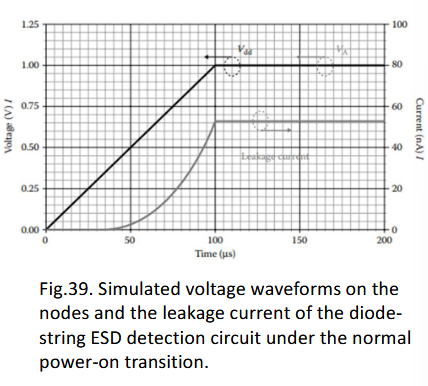

二极管串阈值电压,无电流流经 R, Mp 关闭 &, ,Mn 导通,Vp 降低,SCR 关闭。二极管 有效降低了 Mp 的漏电流。 Vdd 过压 : 二极管串阈值电压,二极管串导通电流,R 两端电压降使 Mp 导通,Vp 高,SCR 导通 . Vss 欠压 (更负的 Vss ): Vdd – Vss > 二极管串阈值电压,二极管串导通电流,R 两端压降使 Mp 导通,Vp = 高,SCR 导通。 在电路正常工作时, Vdd 工作电压低于二极管串的阈值电压。因此, 没有电流流过 R, Mp 保持关闭状态。通过在 Mp 漏极与SCR 触发点之间加入二极管 Do 以产生压降, 可有效降低 Mp 的漏电流。在正向至 Vss ESD 应力作用下, 当 Vdd 电压超过二极管串的阈值电压时, 二极管串开始导通部分电流。这导致电阻 R 两端产生压降, 从而开启 Mp 以触发 SCR。图 39 展示了该设计在正常上电过程中的仿真结果。节点 A 的电压成功充电至 Vdd 的电平。因此, Mp 被完全关断, 仿真得到的待机漏电流仅为 52 纳安。

指向原始笔记的链接

Q9 描述传输线脉冲 (TLP) 测试。讨论如何使用 TLP 获得 DUT 的瞬态 I-V 特性。

5.4.5. 传输线脉冲 (TLP) 测试

使用经典模型来表征电路的 ESD 健壮性存在诸多局限性。首要问题在于, 这些模型仅能提供有限的视角, 揭示保护电路的工作原理、失效方式及位置。HBM 等模型的输入脉冲既复杂又极其短暂, 导致电路响应同样复杂且难以测量。尽管测试应力水平与泄漏电流增加的关系已被制成表格, 但 ESD 认证通常只关注泄漏是否超过预定义的失效阈值。简而言之, 经典模型被当作一个黑箱使用 —— 输入电压级刺激, 输出简单的 ” 通过或失效 ” 响应。

传输线脉冲技术是一种相对较新的 ESD 表征方法, 它为揭开这一黑箱提供了途径。自 1985 年首次引入该技术以来, 它已被广泛用于 ESD 电路的表征与设计。 TLP 测量是一种在瞬态事件 (如 ESD ) 时域内测试和研究集成电路技术与电路行为的方法论。除了可以测量三种 ESD 模型波形在电流和时间范围内的电流与电压随时间变化关系外, 还可以测量 TLP (传输线脉冲) 的电流-电压特性。

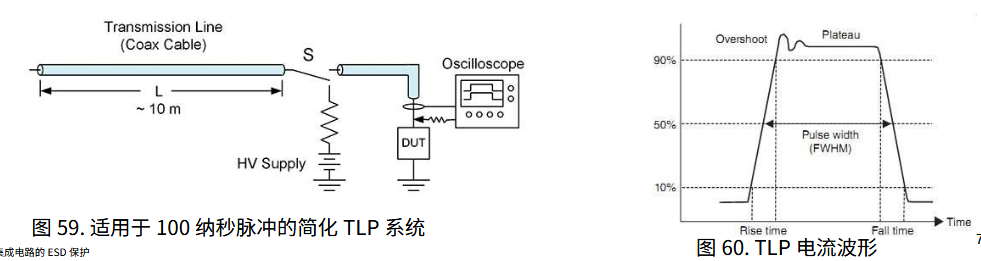

图 59 展示了一个 TLP 实验的示意图, 其中同轴传输线被充电至特定电压后, 向器件的一个 I/O 引脚放电, 同时将地线或电源引脚接地, 其余引脚保持开路。该方法与 HBM 非常相似, 都是对电容器充电后向电路放电。不过, TLP 中的电容是分布式的, 因此会产生简单的方波 (见图 60 )。

TLP 的工作原理是, 一根充电至特定电压的同轴电缆在短路时会输出一个方波脉冲, 其电流等于充电电压除以同轴电缆的特性阻抗, 脉冲持续时间等于电缆传播长度的两倍除以线路的传播速度。例如, 一根 10 米长、 50 欧姆的同轴电缆充电至 100 伏特时, 将产生一个约 100 纳秒、 2 安培的脉冲。

5.4.5.1. TLP 标准要求

- 标准 TLP ( STM5.5.1‐2014 )

- 通常为 0.2 至 10 纳秒的上升时间

- 10 纳秒至 > 毫秒脉冲宽度 (典型值为 100 纳秒)

- 最小 200MHz 带宽示波器

- 最小 200MHz 带宽电压探头

- 最小 200MHz 带宽电流探头。

- 极快 ( vf ) TLP ( SP5.5.2‐2007 )

- 通常 ⇐ 200 ps 上升时间

- 至 10 纳秒脉冲宽度

- 最小 2.5GHz 带宽示波器, 采样率为 5GSa/s

- 最小 1GHz 带宽电压探头

- 最小 2GHz 带宽电流探头

5.4.5.2. 使用 TLP 测量瞬态电流和电压的时间依赖性

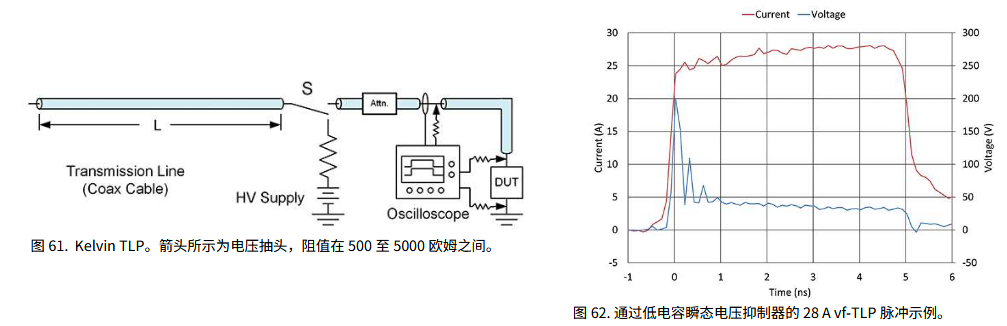

时域瞬态电流和电压可通过图 61 所示的开尔文 TLP 进行测量。

图 62 展示了一个低电容瞬态电压抑制器 ( TVS, 即专为保护电子设备免受过压而设计的齐纳二极管) 对 28A vf‐TLP 脉冲时间依赖性的测量示例。该 5 纳秒长的电流脉冲形态良好, 上升时间仅为纳秒的一小部分。TVS 器件在 1 纳秒内将电压钳制在 5V 以下。

5.4.5.3. 使用 TLP 测量瞬态 I-V 特性

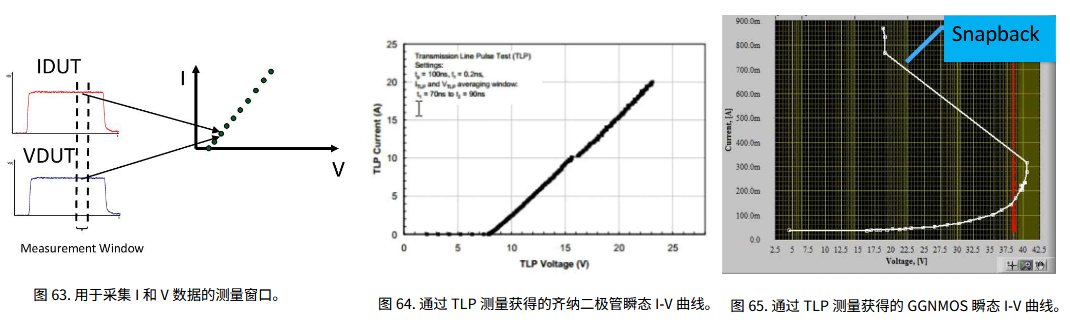

TLP 最明显的应用是提取保护器件的瞬态电流-电压 ( I‐V ) 曲线。通过对电路施加一系列递增的输入电压脉冲, 并绘制器件电压与电流的对应点, 即可生成特征 IV 曲线。与传统曲线追踪仪不同 —— 后者因施加相对较长的阶梯应力会导致破坏性发热, TLP 的短脉冲特性使其能在不造成热损伤的前提下, 提取极高电流水平下的 IV 数据点。当然, 应力间隔时间需确保充分的热量消散,一两秒已绰绰有余。保护器件的瞬态 I‐V 曲线极具信息价值, 它能直观展现器件在 ESD 应力期间的动态响应。诸如开启电压、维持电压及二次击穿触发电流等关键参数, 均可直接从曲线上读取。尽管方波输入并不能精确模拟任何可能的 ESD 事件, 所得 I‐V 曲线的参数可以与 “ 真实 ”ESD 应力的敏感性以及诸如 HBM 等测试相关联。

测量窗口通常位于 70% 至 90% 的区域, 以获取 I‐V 曲线的一个点, 如图 63 所示。图 64 和图 65 分别展示了齐纳二极管和 GGNMOS 的瞬态 I‐V 特性曲线。

指向原始笔记的链接