Q1

Q2

4.3. 闩锁的原因

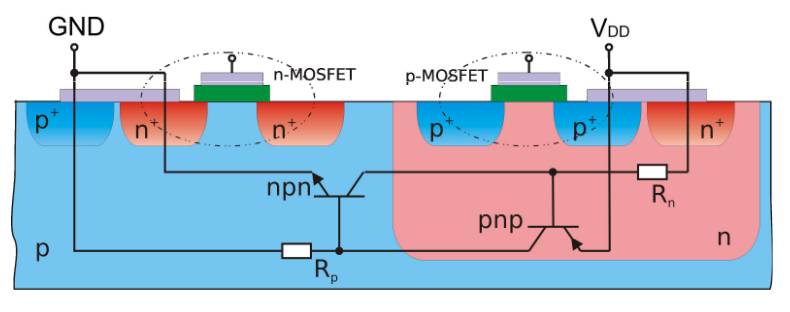

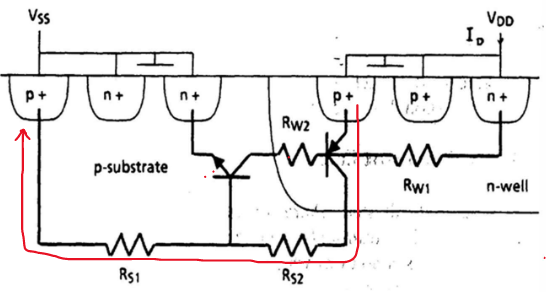

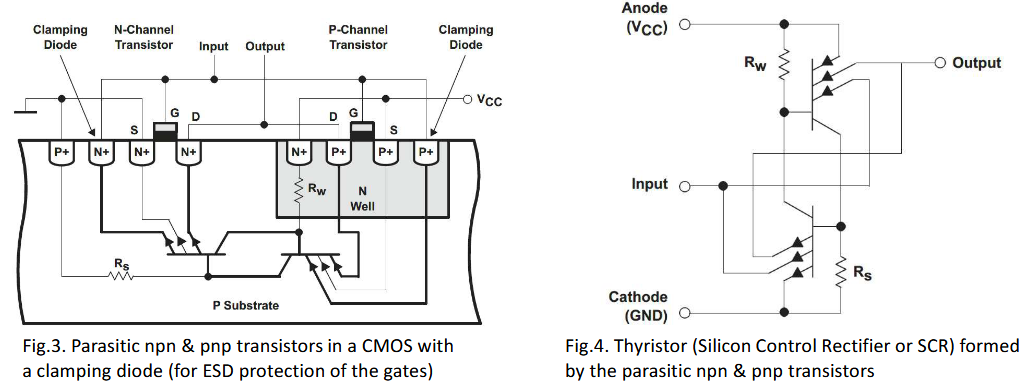

参见图 3 和图 4。当寄生晶闸管(寄生 npn 和 pnp BJTs+井电阻 Rw 和衬底电阻 Rs)以各种方式触发时,就会发生闩锁,如下所述。

闩锁触发原因总结

- 输入或输出电压高于电源电压(过压)或低于地电平/衬底电位(欠压);

- ESD 或者高电源电压击穿晶体管;

- 衬底电流和阱电流导通寄生 BJT。

如果输入或输出电压高于电源电压(过压) 或低于地电平/衬底电位(欠压),电流会注入晶闸管(寄生 SCR 结构)的栅极。若电流的幅度和持续时间足够,晶闸管将被触发。寄生晶体管的渡越频率仅约 1 MHz,因此仅持续几纳秒的过压/欠压(如电路板上的信号反射)通常不足以触发闩锁。但对于数米长的导线或持续时间更长的过冲,必须考虑晶闸管被触发的可能性。这一风险同样存在于芯片与外部世界的接口处,此处常出现不可接受的过压。

静电放电(ESD) 可能触发寄生晶闸管。即使放电持续时间仅几十纳秒,整个芯片可能被载流子淹没,这些载流子缓慢泄放,最终导致晶闸管触发。过高的电源电压(远超出数据手册额定值)也可能触发晶闸管。此时,电源电压需升至晶体管的击穿电压。在击穿状态下,本应截止的寄生晶体管电流会因雪崩效应激增,从而激活晶闸管。

如同前面所言,当

和 当满足以下条件时,衬底电流和阱电流足以导通寄生 NPN 和 PNP 双极晶体管。 衬底/阱电流的产生原因包括:

- 瞬态位移电流(电源或地的突然瞬变);

- 辐射(X 射线、宇宙射线或α粒子)在衬底和阱区产生足够电子-空穴对;

- 阱结的漏电流导致较大的横向电流;

- 阱结反向偏压过大引发的雪崩击穿;

- 热载流子效应。

4.3.1. 闩锁问题的分类

闩锁问题主要分为两类:

指向原始笔记的链接

- 内部闩锁(ILU):由内部电路引起,如电源弹跳、片上传输线反射或载流子生成,触发体硅 CMOS 中的寄生 SCR。

- 外部闩锁(ELU):由 I/O 电路接收的片外信号触发,这些信号产生大幅电压波动或载流子注入。若载流子未限制在 I/O 单元内,可能触发 I/O 电路或邻近内部电路中的闩锁。

Q3

4.2.3. 闩锁触发的必要和充分条件

参考图 1,当只考虑 BJT 时,可以找到闩锁的必要条件。因为 pnp 的基极连接到 npn 的集电极,npn 的基极又连接到了 pnp 的集电极,由此两个双极晶体管形成一个反馈回路,回路增益等于 beta 积

。 和 分别是 PNP 和 NPN 晶体管的共发射极电流增益。如果环路增益小于 1,则 会衰减为 0。npn 和 pnp BJT 均关闭。因此,不会触发闩锁。要获得正反馈,环路增益必须大于 1 。通过减小共基极增益就能提高对闩锁的抗性。 [! tldr] 闩锁触发的必要条件 即回路增益

参考图 2,BJTs 和衬底和井电阻都被考虑在内,可以找到必要和充分的条件进行闩锁。由电子构成的 npn 集电极电流

不会完全流入 pnp 基极,因为它的一部分通过井电阻 ( ) 分流到 n+ 井触点。该电流表示为 。剩余电流 成为 pnp 基极电流。因此,pnp 集电极电流为 。同样,一部分 pnp 集电极电流 通过衬底电阻 分流到衬底触点。流入 npn 基极的反馈电流现在是 IRS 偏移的 pnp 集电极电流,即 。 所以为了形成正反馈,进入 npn 基极的电流必须大于原本的 npn 的基极电流。

同时,总电流又能表示为

,将这个代入不等式中就能得到, CMOS 闩锁发生的充分必要条件式

指向原始笔记的链接 这个就是触发 CMOS 闩锁的必要充分条件。相较于必要条件,更多地考虑了 n 阱电阻和 p 衬底的电阻。

, 是 npn 的基极-发射极电压; , 是 pnp 的基极-发射极电压。 所以根据不等式,如果想要避免闩锁,要么降低 npn 和 pnp 的共基极增益,要么就增加打开 npn 和 pnp 所需要的

和 。 当

指向原始笔记的链接和 时,npn 和 pnp 就会打开。这意味着,为了避免闩锁,应降低在 npn / pnp 区域中基底电阻和井电阻以及基板电流和井电流。

Q4

施加

施加

Q5

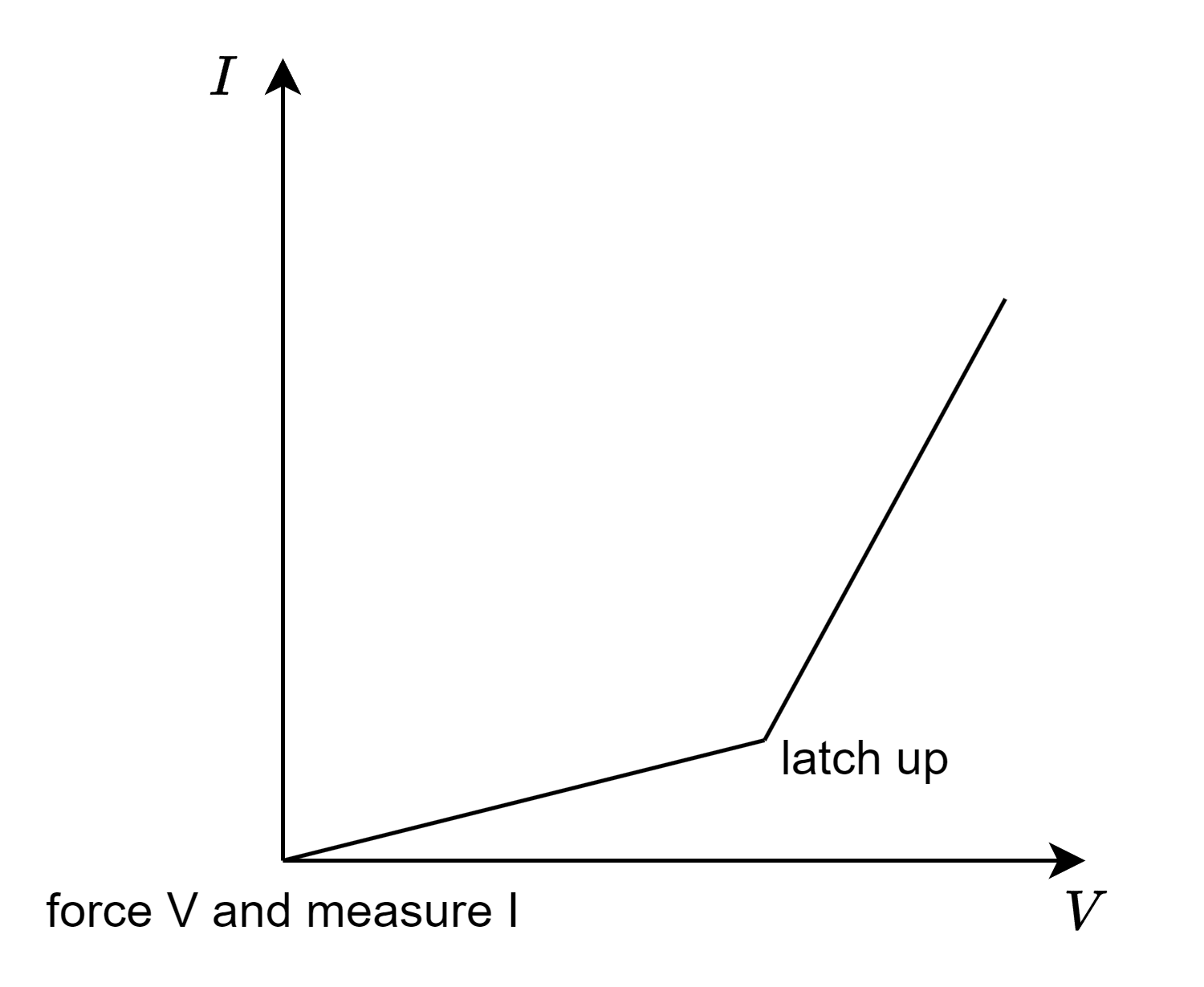

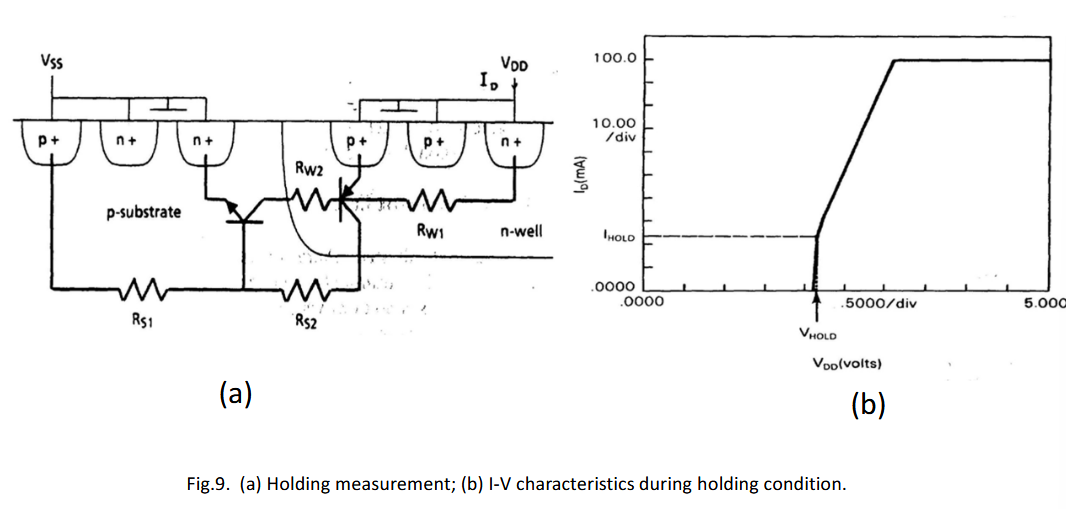

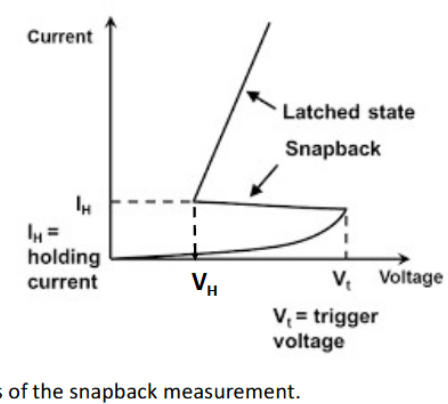

4.4.5. 保持特性表征:回滞测量

测试配置(参见图10 (a)):采用恒流源激励并测量电压。I-V特性曲线(图10 (b))可确定:保持电流

和保持电压 。

指向原始笔记的链接[! note] 施加

测量 的图像

Q6

Experiment design by Prof. Deepseek

7. Measure I-V characteristics to identify trigger/holding points

8. From snapback curve, estimate Rₛ and R_w from voltage drops

9. Use separate measurements of isolated BJTs to estimate α’s

10. Alternatively, measure sensitivity to well/substrate bias to extract parameters

11. Use curve fitting with latchup equations to extract parameters

Q7

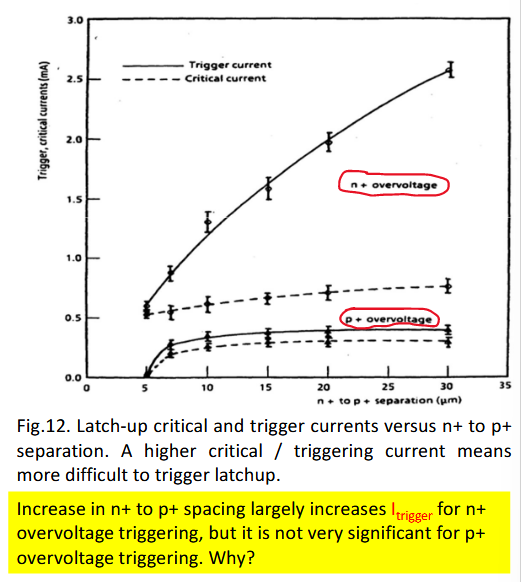

4.5.1.1. 降低环路增益

通过增加 NMOS 到 PMOS 的间距来减小

和 。间距增加,npn 和 pnp 的基极宽度增加,电流增益就下降了。

闩锁对 n+ 到 p+ 间距具有依赖性。下图显示了 p+ 和 n+ 过压感应触发的触发电流和临界电流与 n+ 到 p+ 分离的关系。对于 n+ 过电压应力,触发电流随着 n+ 到 p+ 分离的扩大而迅速增加。随着 n+ 到 p+ 间距的增加,

减小,因此 增加。

其实从 npn 和 pnp 的位置就能看出来,n+和 p+的间距对横向的 npn 的

影响最大,对于纵向的 pnp 的 的影响不大。 指向原始笔记的链接[! question] 为什么增加 n+ 到 p+ 的间距会增加 n+ 过压触发的触发电流而对 p+ 过压触发的触发电流影响不大 n+过压触发依赖于横向NPN管(n+发射极 → p衬底基极 → n阱集电极), 该NPN的基区宽度直接由n+到p+的间距决定。p+过压触发依赖于纵向PNP管(p+发射极 → n阱基极 → p衬底集电极),该PNP的基区宽度主要由n阱深度决定,与n+到p+的横向间距无关。

Q8

如果是 p+ 过压触发,

如果是 n+ 过压触发,

代入题目条件进行运算即可。

Q9

![[《IC Tech》笔记#4512-降低-r_w-和-r_s-来提高触发电流|4.5.1.2. 降低

Q10

4.5.5. 策略 5:大闩锁保护窗口

通过增加保持电压

来增加闩锁保护窗口。

这里

是 p+基底和延展层的电阻的和 。 是 n+和 n 阱之间的电阻。

是PNP管的集电极-发射极饱和压降(通常≈0.1~0.3 V)。 是NPN管的基极-发射极导通电压(≈0.7 V)。 所以增加

就是增加 n+到 n 阱的间距;减小 就是减小延展层厚度和用重掺杂 p+基底。 也可以通过降低

来增加闩锁保护窗口。在低功耗 CMOS 电路中, 小于 0.7 V 的 CMOS 工艺不受闩锁的影响,因为 npn 和 pnp BJTs 从未有过大的基极到发射极电压 来开启。随着 CMOS 技术已缩小到 5 nm 节点以用于低功耗应用,核心电路的 已降低到 1 V 以下。在 < 1 V 的应用中,由于 通常高于 ,因此不会持续闩锁,在这种情况下闩锁风险最小。但是,内核电路可以在过驱动模式下工作(例如,在瞬态条件下),或者 I/O 电路在 > 1 V 的正常工作电压下工作。在这种情况下,当 低于 时,可能会考虑持续闩锁,因此需要适当的闩锁预防。 指向原始笔记的链接[! question] 解释为什么如果保持电压大于电源电压,则无法维持闩锁。建议一种提高保持电压的有效方法。 当保持电压大于电源电压的时候,即使触发闩锁,电源电压也无法维持

和 ,导致寄生晶体管截止,闩锁无法持续。 提高保持电压可以从 和 两个电阻入手。通过使用重掺杂 p+ 衬底和使用薄外延层能减小 ;通过增加 n+ 到 n 阱之间的距离能增加 。

测试配置(b)回滞I-V特性曲线.png)