1. 同步策略

1.1. 同步

同步即确定事件的顺序,确保信号在不同时钟域或异步环境中可靠传输。

同步可以用于:

- 使用时钟对异步输入进行采样

- 跨时钟域处理。使用不同时钟对同步信号进行采样,若两时钟均为周期性信号, 则此问题较易解决;

- 异步信号仲裁。共享资源的请求线路。

1.2. 同步失败

同步失败,或者说同步器进入亚稳态,指随着两个输入信号之间的时间差

当同步失败的时候就需要进行仲裁。通过仲裁结果确定事件顺序。

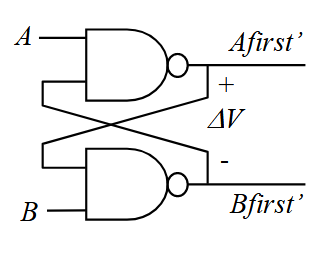

1.2.1. NAND 仲裁器

NAND SR 锁存器,其具有以下特性:

- 如果 A 比 B 早到很多, A 优先会变低并锁定 B;

- 如果 B 比 A 早到很多, B 优先会变低并锁定 A;

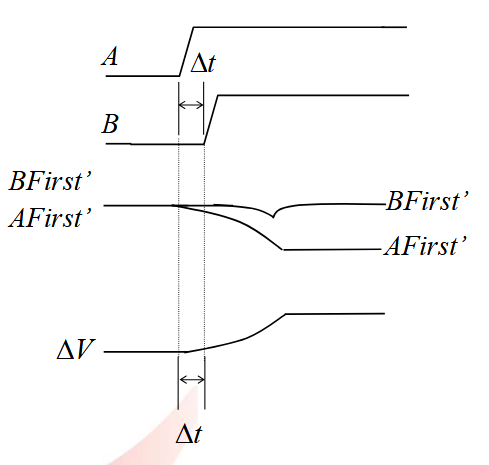

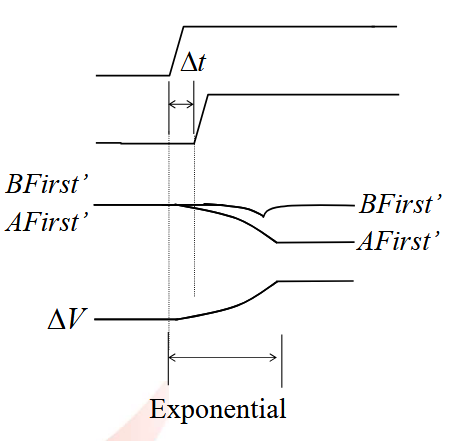

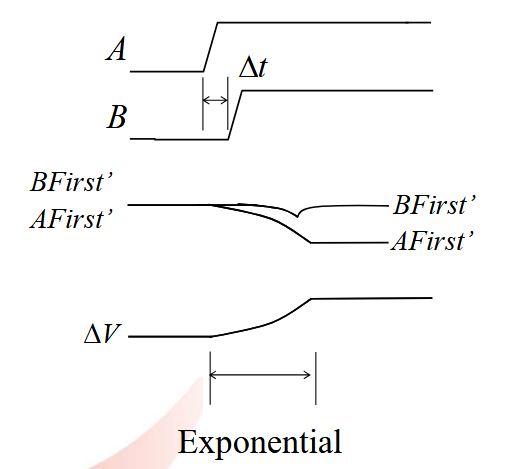

1.2.1.1. 动态分析

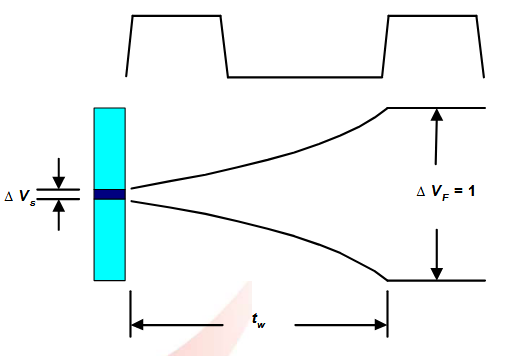

如果 AB 几乎同时升高,初始输出电压的差异与时间差成正比。

当 AB 信号继续升高的时候,初始电压

这样就能得到 NAND 仲裁器的动态稳定时间

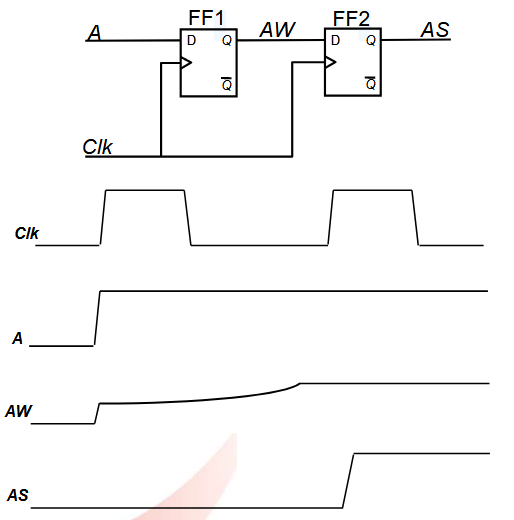

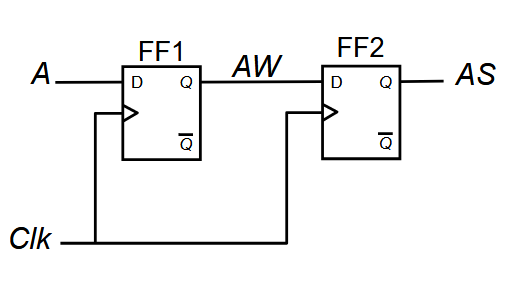

1.2.2. 暴力 (等待) 同步器

使用 clk 信号对异步信号进行采样,通过触发器 FF1 后,信号可能进入亚稳态,在时间

如果 FF2 触发的时候,AW 仍然在亚稳态,这样的情况发生的概率有多大?

1.3. 故障概率

1.3.1. 进入亚稳态的概率

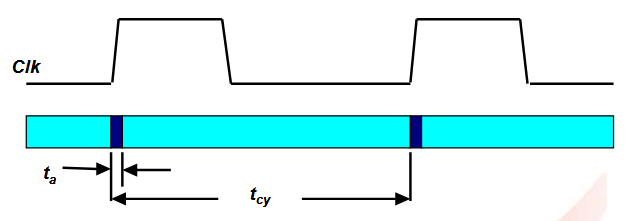

如果输入信号在触发器的孔径时间 aperture time (ta) 期间转换,则 FF1 可能会进入亚稳态。给定转换处于孔径时间内的概率, 即孔径时间所占的时间比例。

1.3.2. 停留在亚稳态的概率

如果初始电压差太小,在等待期间无法呈指数放大,则仍处于亚稳态。以该电压开始的概率是总电压范围中 “ 过小 ” 部分所占的比例。

1.3.3. 故障概率与失败频率✨

错误概率为,

失败率 failure rate为,

等待同步器失败率

指向原始笔记的链接

为输入信号频率; 为时钟频率; 为孔径时间; 为时钟周期; 为再生时间(时间常数)。

同步失败之间的平均时间(MTBF)为

孔径时间

Flip-Flop 的孔径时间,

即孔径时间是 Flip-Flop 的建立时间和保持时间的和。

等待时间

如果继续增加级数,相当于增加了

,即给亚稳态增加了衰减时间。

- 第一级:决定系统进入亚稳态的初始概率。

- 后续级:通过延长衰减时间指数级降低失败概率。 所以总的等待时间

为级联触发器总级数; 为时钟周期; 为 FF 建立时间; 为触发器时钟到输出延迟。

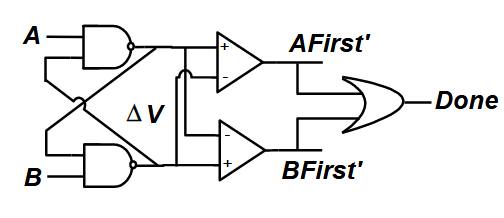

1.4. 完成检测

无法限定同步器稳定所需的时间,然而, 确实有可能检测到同步器何时稳定下来。这只有在后续逻辑能够利用这个异步完成信号时才有用。

1.5. 同步层次结构✨

同步的难度取决于信号事件与时钟事件之间的关系。

- 同步。信号事件总是发生在时钟禁止区域之外,例如相同时钟。

- 等时同步。信号事件以相对于时钟固定但未知的相位发生。例如同频时钟;

- 准同步。信号事件的相位随时间缓慢变化,例如略微不同的频率时钟;

- 周期性。信号事件是周期性的,包括等时和准同步,信号同步至一些周期性时钟

- 异步。信号事件随时可能发生。

同步层次摘要

| 类型 | 频率 | 相位 |

|---|---|---|

| 同步 Synchronous | 相同 | 相同 |

| 等时同步 Mesochronous | 相同 | 持续 |

| 准同步 Plesiochronous | 稍微不同 | 缓慢变化 |

| 周期同步 Periodic | 不同 | 周期变化 |

| 异步 Asynchronous | 随机 | 任意的 |

2. 同步器设计

2.1. 等时同步器

信号与时钟之间的相位差恒定,典型例子是分发主时钟且存在一定时钟偏移的系统。由此只需要同步一次即可。在复位期间检查相位,如果正常, 则直接对信号持续采样;如果异常, 则在延迟后对信号持续采样。此相位检查是我们唯一采样的异步事件,可以很长时间才采样一次。

同步器之间的比较:

- 同步延迟(除了所需的

); - 故障率。

2.1.1. 暴力同步器

同步延迟:

等待同步器失败率

指向原始笔记的链接

为输入信号频率; 为时钟频率; 为孔径时间; 为时钟周期; 为再生时间(时间常数)。

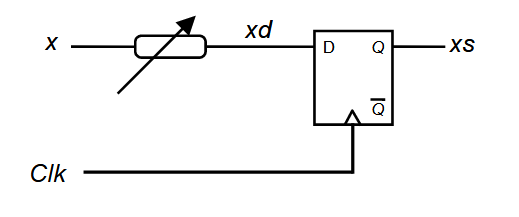

2.1.2. 延迟线同步器

对于准时同步和准同步信号,根据需要来延迟信号, 以确保同步器时钟外的转换,我们如何设置延迟线? 这个同步器的延迟是多少?

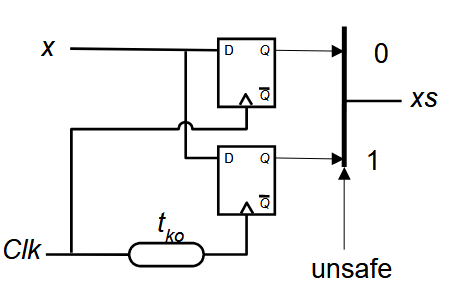

2.1.3. 双寄存器同步器

延迟线同步器成本高昂, 我们需要为每个输入配备一条延迟线;我们延迟时钟而非数据,使用正常和延迟时钟对数据进行采样,选取 “ 安全 ” 输出。可以通过双寄存器解决。

要判断信号是否不安全, 观察它是否在禁止区域内发生变化,在禁区前后采样并查看结果是否不同。这些样本可能导致触发器进入亚稳态,需要等待此状态至衰减。如果是等时同步, 我们可以等待很久很久了, 因为我们只需要做这一次。

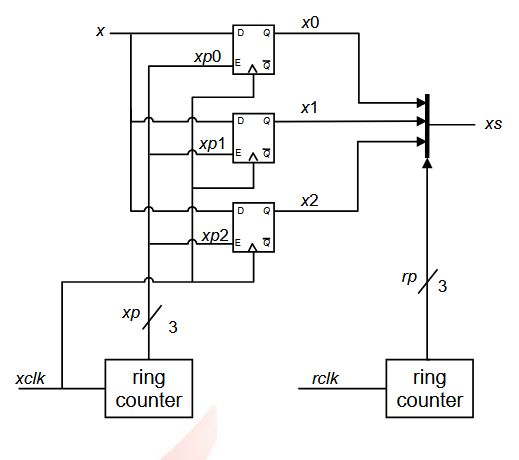

2.1.4. FIFO 同步器

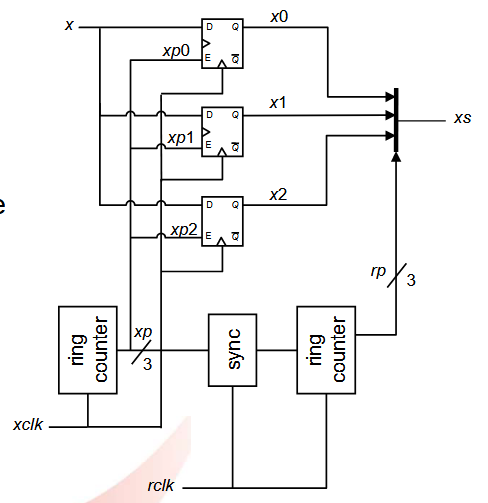

可以使用先进先出 (FIFO) 缓冲将同步信息移出数据路径。在一个时钟域 (xclk) 中将数据同步到 FIFO;在另一个时钟域 (rclk) 中将数据从 FIFO 复用输出。同步信息移到了哪里?如何初始化指针?

2.2. 准同步同步器

采用准同步时序时, 一个时钟比另一个时钟运行得稍快。相同的基本同步器类型适用,例如暴力、延迟线、双寄存器、先进先出 ( FIFO )。准同步需要定期重新同步,并且需要流量控制。

2.2.1. 准同步 FIFO 同步器

使用发送时钟 (xclk) 插入数据;使用接收时钟 (rclk) 移除数据;通过将发送指针 (xp) 同步到接收时钟来定期更新接收指针 (rp)

- 我们如何知道何时执行此操作?

- 如果在更新接收指针 (rp) 时,rp 的值增加了2 或 0,我们该怎么办?

2.2.2. 时钟上的相位滑移检测指针

在跨时钟域同步(尤其是准同步系统,即Plesiochronous Systems)中,相位滑移(Phase Slip) 是指由于发送端和接收端时钟频率的微小差异(如±200ppm),导致数据指针(如FIFO的读写指针)逐渐偏移,最终发生跳变(Skip)或重复(Duplicate)的现象。

相位滑移检测指针是用于动态监控和修正这种偏移的机制,确保数据在跨时钟域传输时不丢失或重复。

(1) 指针的时钟比喻

- 将发送指针(xpxp)和接收指针(rp)视为表盘上的两根指针:

- xp:以发送时钟 xclk 移动(如“分针”)。

- rp:以接收时钟 rclk 移动(如“时针”)。

- 相位滑移:两根指针的相对位置随时间缓慢变化(因频率差异)。 (2) 检测方法

- 动态相位窗口:

接收端会定义一个安全相位窗口(如 rp与 xp 的允许最大偏移角度)。- 当 xp 和 rp 的相位差超出窗口时,触发滑移检测。

- 指针更新策略:

- 正常情况:rp 每次递增1(读取一个数据)。

- 滑移时:

- 频率较快:rp 可能跳过1个位置(如从2直接到4)。

- 频率较慢:rp 可能重复1个位置(如两次读取位置3)。

2.3. 周期同步

发送和接收时钟是周期性的, 但频率不相关。在这种情况下,单次同步不会永远持续 (如同步的) 甚至不会维持很长时间 (如准同步的)

2.3.1. 周期性同步器

如果输入信号与某个周期性时钟同步, 我们就能预测其事件允许发生的时间任意远的未来。因此, 我们可以提前确定信号在给定时钟周期内采样是否安全,如果是的话, 我们只需对其进行采样;如果不是, 我们延迟信号 (或时钟) 以确保安全。

这使我们能够将等待时间 tw 移出关键路径之外。我们可以将其做得很长而不增加延迟

2.3.2. 时钟预测器电路

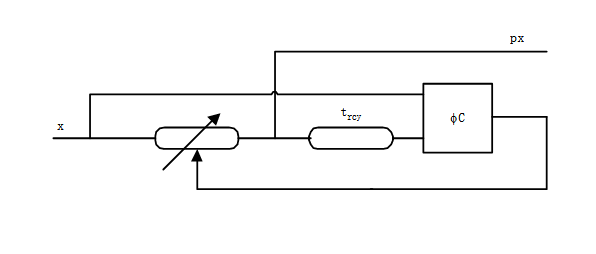

假设我们想知道输入 x 在未来的一个 rclk 周期 ( trcy ) 后的值,这只是 txcy– trcy 的一个相位偏移。

假设我们想知道输入 x 在未来的一个 rclk 周期 ( trcy ) 后的值,这只是 txcy– trcy 的一个相位偏移。

利用简单的定时循环很容易产生这种相移。注意, 我们同样可以轻松预测 xclk 几个 rclk 周期后的情况。

3. 异步器设计

大多数情况下, 我们仅将事件与时钟同步 —— 不论是在时钟 i 还是 i +1 上处理该事件都无关紧要。我们可以通过异步处理事件来避免这种不必要的同步,事件的到来会触发它的处理。

3.1. 异步协议

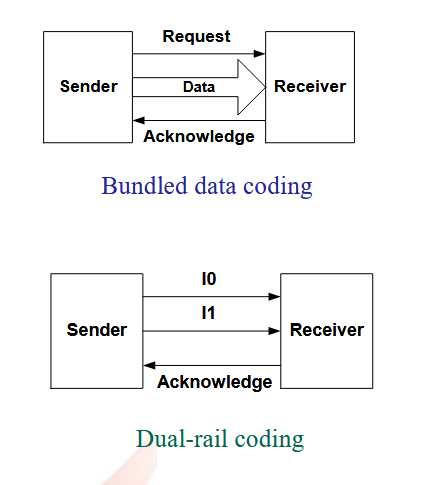

由于缺少全局时钟,握手协议用于同步:

- 2 相

- 边缘敏感

- 捆绑数据编码

- 4 相(归零)

- 电平敏感

- 双轨编码

3.2. 异步数据编码

由于缺乏全局时钟, 异步数据必须附带时序信息表示。

- 捆绑数据 (单通道) 编码, 1 根线代表 1 位信息;

- 双轨编码,用两根导线表示 1 位信息;