1. CMOS 延迟估计

通过建立一个简单的模型,利用 R 和 C 来估计 CMOS 的延迟。

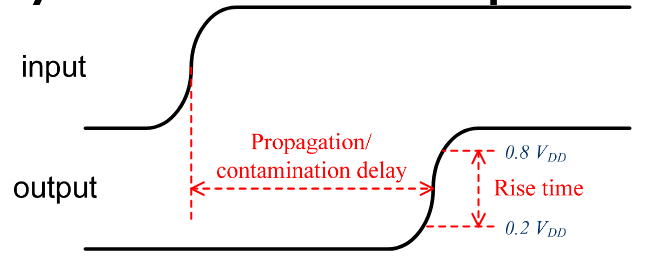

1.1. 延迟的定义

取平均可以得到传播延时和污染延时,

[! note] 如何找到污染延迟 污染延迟就是最短的传播延迟,例如并联的两个晶体管串联一个电容时,两个同时开启将电容充满的时间最短。

1.2. 延迟估计

核心公式就是

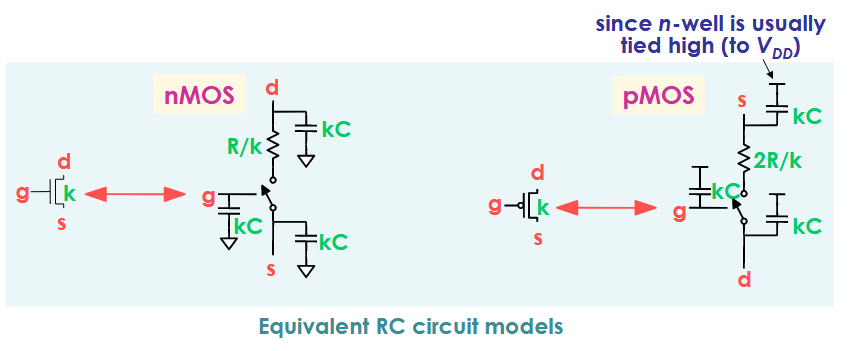

1.3. 开关级 RC 延迟模型

我们使用理想的开关模型来对 MOS 建模,

- 单位 NMOS 有电阻 R 和电容 C

- 单位 PMOS 有电阻 2R 和电容 C

在栅极、漏极、源极都会有一个接地的电容(PMOS 的电容连接的是虚拟地)。

在栅极、漏极、源极都会有一个接地的电容(PMOS 的电容连接的是虚拟地)。

k 是 MOS 管相对于单位 MOS 管的大小。 假设:

- 串联的晶体管之间只用画一个电容(源漏相接只考虑一个电容);

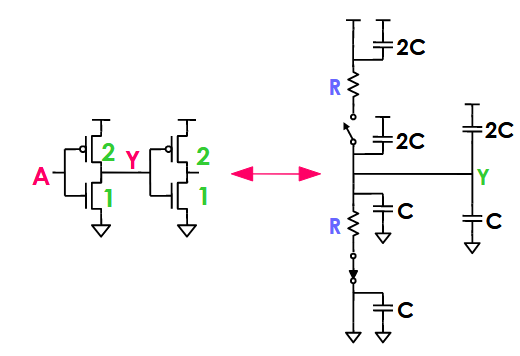

简化 RC 电路模型:

- 在

和 被短路的电容需要除去; - 连接到同一个输出的并联电容需要合并;

- 连接到同一个输入的并联电容需要合并;

1.4. 单位反相器延迟的估计

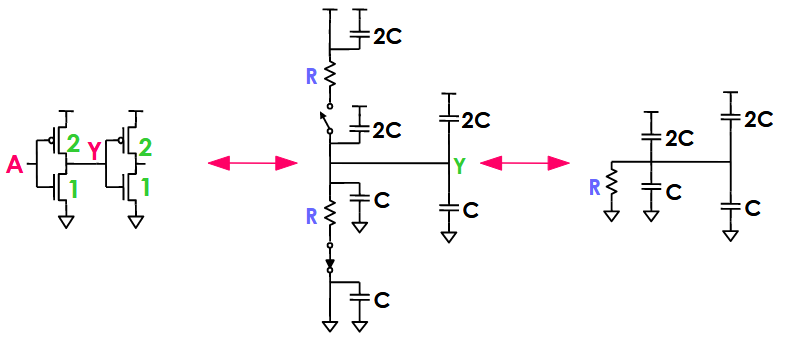

显示第一个反相器驱动第二个反相器栅极的等效电路。因为我们考虑的是驱动情况下,所以不考虑第一个的栅极电容和第二个的扩散电容。可以看出,单位反相器具有相同的上升和下降电阻,因此具有对称的上升和下降时间。

显示第一个反相器驱动第二个反相器栅极的等效电路。因为我们考虑的是驱动情况下,所以不考虑第一个的栅极电容和第二个的扩散电容。可以看出,单位反相器具有相同的上升和下降电阻,因此具有对称的上升和下降时间。

假设此时输入一个高电平,画出对应的模型并简化,

得到传播延迟

1.5. 如何计算 MOS 尺寸 k

在计算 MOS 尺寸 k 的时候,需要考虑的是最坏情况,也就是传播延时。并且 CMOS 电路的上升和下降阻抗需要和单位反相器的上升和下降阻抗相同。

例如,PDN 是 3 个串联的 NMOS,则每个的尺寸 k 需要为 3,PDN 的电阻

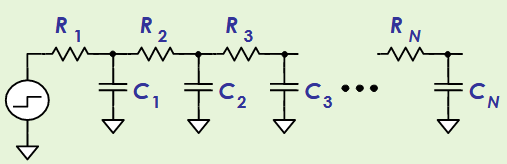

1.6. Elmore 延时模型

有延时为,

有延时为,

由此就能估计节点

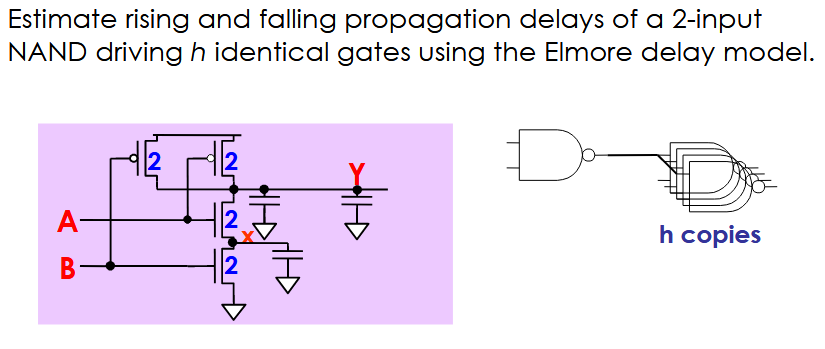

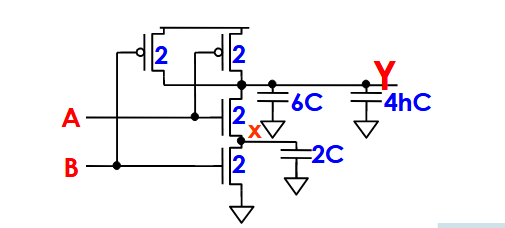

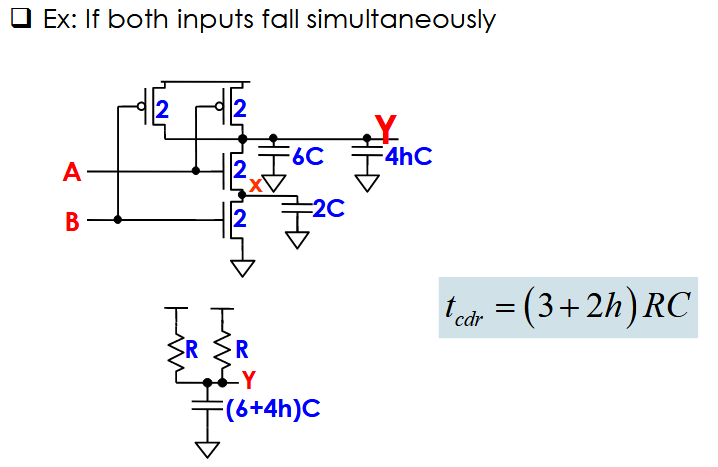

1.7. Example: 2-input NAND

这个例题可以用来实战演练一下。

这个例题可以用来实战演练一下。

1.8. 延迟的构成

延迟主要由两个部分构成,

- 寄生延迟,与负载无关

- 努力延迟,与负载电容成比例

1.9. 最好和最坏情况下的延迟

在最坏的情况下,输入 A 已经为“1”,因此节点 x 通过顶部 pMOS 晶体管充电至接近 VDD。输入 B 上升,打开底部 nMOS,并对节点 x 上的电容和输出充电。门的最佳情况延迟(污染延迟)可以大大减少,如何实现?

1.10. 污染延迟

最佳情况(污染)延迟可能远小于传播延迟。

因此,为了获得最快的响应,在可行的情况下,最晚的输入应连接到最靠近输出节点的晶体管。

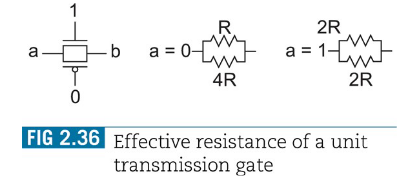

1.11. 单位传输门延迟的估计

晶体管的有效电阻在其不良方向上通过的值更大。例如,单元 nMOS 晶体管通过“1”的有效电阻可以建模为 2R,单位 pMOS 晶体管通过“0”的有效电阻可以建模为 4R。

可以发现,无论传输“0”还是“1”,有效阻抗都是接近 R。

可以发现,无论传输“0”还是“1”,有效阻抗都是接近 R。

请注意,传输门通常使用大小相等的 nMOS 和 pMOS 晶体管构建。增大 pMOS 尺寸仅能略微改善电阻,但会显着增加电容。

2. CMOS 功耗

2.1. 功率和能量

电源从连接到芯片 VDD 引脚的电压源获取。

瞬时功耗:

2.2. CMOS 电路中的功耗

主要来源于 1) OFF 晶体管中的亚阈值传导 2) 通过栅极氧化层的隧道电流 3) 通过反向偏置二极管的泄漏 4) 比率电路中的竞争电流。 主要来自于 1) 负载电容的充电和放电 2) pMOS 和 nMOS 网络部分导通时的“短路”电流。

2.3. 静态功耗

零静态功耗是 CMOS 的主要优点。二次效应会导致少量静态电流流过电路。即使芯片处于静态状态,也会消耗静态功率。比率电路在导通晶体管之间的竞争中消耗功率。泄漏从名义上关闭的器件汲取功率。静态功耗成为 130 nm 及以上工艺的主要设计问题。

2.4. 动态功耗

假设系统时钟频率为 f,

- 如果信号是时钟,

- 如果信号每个周期切换一次,

- 动态门:每个周期切换 0 或 2 次,

- 静态门:取决于设计,但通常

2.5. 低功耗设计

降低静态功耗:

- 选择性地使用比率电路

- 选择性地使用低 Vt 器件

- 减少漏电:堆叠器件、体偏置、低温

降低动态功耗:

:时钟门控、睡眠模式 - C:小型晶体管(尤其是时钟上),短线

:最低合适电压 - f:最低合适频率