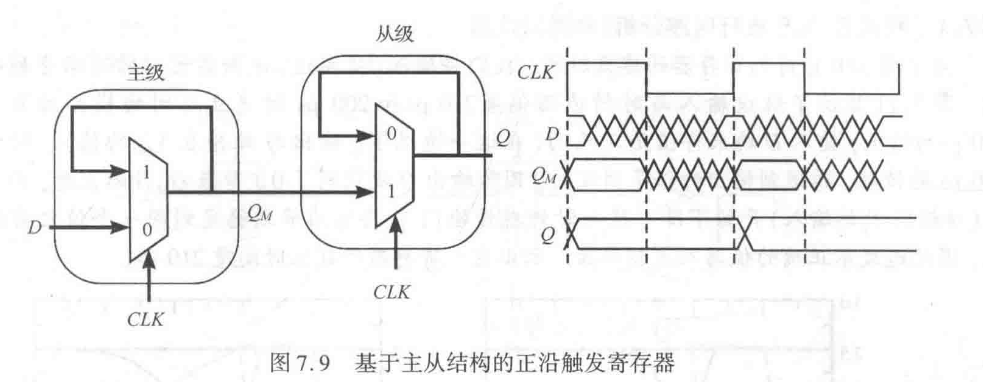

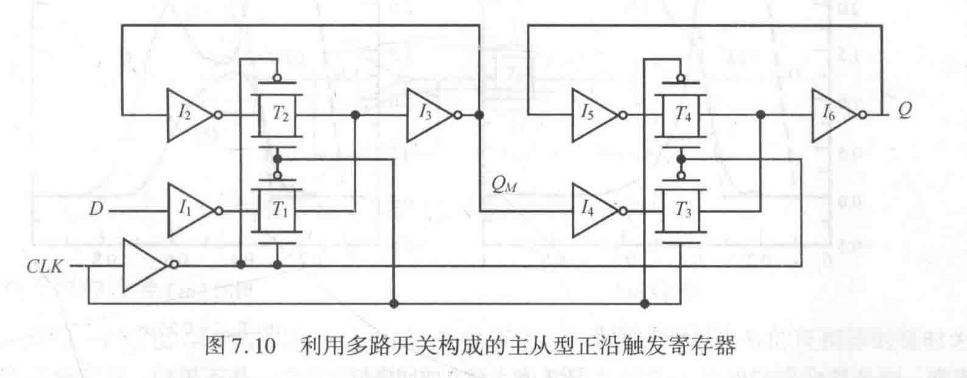

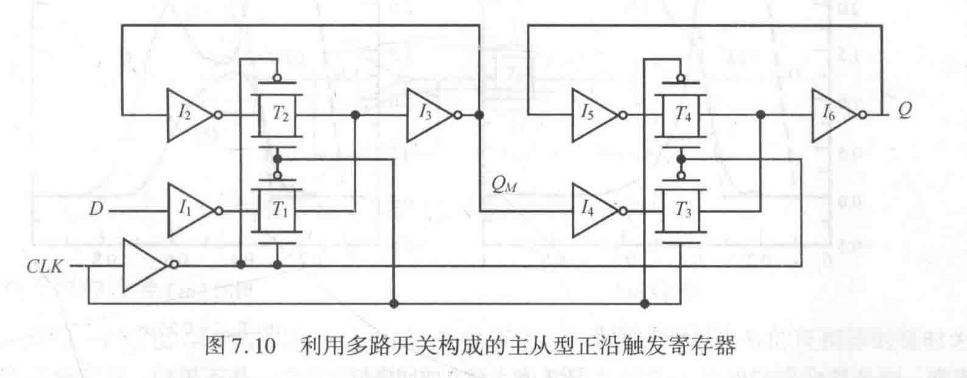

主从结构是构成边沿触发触发最常见的方法。存器由一个负锁存器 (主级) 串联一个正锁存器 (从级) 构成。本例采用的是多路开关型锁存器, 但实际上可以采用任何类型的锁存器。

主级是负锁存器,从级是正锁存器。这样就能实现正沿触发效应。负沿触发交换两个锁存器的位置即可实现。在低电平的时候,

工作流程

上图是一个完整的主从正沿触发寄存器的晶体管级实现。多路开关采用上一节讨论过的传输门来实现。当时钟处于低电平时 (

有点繁复,简化一点就是,低电平时主级透明,从级维持;上升沿时,主级高电平主级维持,从级透明。

[! question] 这里我没有讨论上升沿和下降沿的情况,虽说说明了是上升沿寄存器,但是还是没有理得很清楚。

时序特性

寄存器有三个重要的特征时序参数: 建立时间、维持时间和传播延时。

假设每一个反相器的传播延时为

对上面这个电路来分析寄存器的三个时序参数。

建立时间是输入数据 D 在时钟上升沿之前必须有效的时间。否则在时钟上升沿时,从级无法采样到信号 D。当信号为低电平时,主级透明,信号 D 需要传到