1. 可测试性设计 DFT

如果存在一个明确规定的程序来暴露一个故障,那么它是可测试的,且该程序利用现有技术能以合理成本实现。当针对某个故障集中的每一个故障都是可测试的时, 称该电路相对于该故障集是可测试的。

可测试性设计 ( DFT ) 是指那些使测试生成和测试应用具有成本效益的设计技术。

电子系统包含三类组件: (a) 数字逻辑、 (b) 存储模块, 以及 (c) 模拟或混合信号电路。在本章中, 我们讨论数字逻辑的 DFT 技术。

可测试性的重要因素

- 可控性: 衡量控制一条线路的难易程度。

- 可观测性: 衡量在 PO 处观察线路的难易程度。 一般来说, DFT 研究的是提升可控性与可观测性的方法

与 DFT 相关的成本

- 引脚

- 面积/产量

- 性能

- 设计时间

1.1. 临时可测试性设计 Ad Hoc DFT

将大型电路划分为较小的子电路, 以降低测试生成成本 (采用多路复用和 / 或扫描链技术)。

插入测试点以增强可控性与可观测性。测试点: 控制点(强制信号值)与观测点(直接观察内部节点)。

常见技术: 设计易于初始化的电路;提供逻辑以切断全局反馈路径;将大型计数器分割为较小的计数器;避免使用冗余逻辑;将模拟电路和数字电路物理隔离;避免使用异步逻辑;考虑测试需求 (引脚限制等),等等。

临时 DFT 的问题在于:

- 大量的 I/O 引脚;

- 可以通过添加多路复用器来缓解;

- 测试时间过长;

1.2. 结构方法

结构方法对电路划分很有效,并且为测试提供了内部状态变量的可控性和可观测性。结构方法将顺序测试问题转化为组合问题。

四大主要方法:

- 移位寄存器修改

- 扫描路径

- 电平敏感扫描设计 ( LSSD )

- 随机访问

电路会采用预先指定的设计规则进行设计。

1.2.1. 扫描设计 Scan

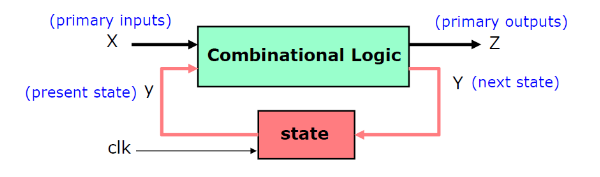

扫描设计就是将时序电路的测试转化为组合逻辑测试,考虑一个时序电路的表示

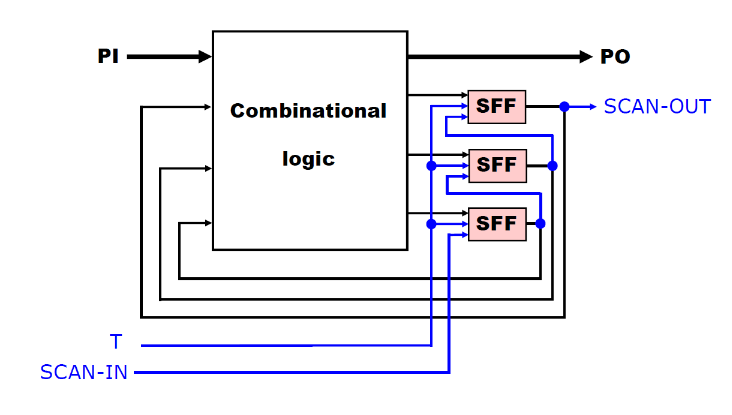

为了使状态向量的元素可控且可观测, 我们添加扫描链,包括以下组件:

- 测试模式引脚 (T)

- 扫描输入引脚 ( SI )

- 扫描输出引脚 ( SO )

- 每个触发器前的多路复用器 (开关)( M )

1.2.1.1. 扫描测试生成与设计规则

ATPG:自动测试模式生成

测试模式生成: 使用组合 ATPG 生成针对组合逻辑中所有可测试故障的测试向量;添加移位寄存器测试, 并将 ATPG 测试转换为扫描序列以用于生产测试。

扫描设计规则:

- 所有状态变量仅使用时钟控制的 D 型触发器;

- 至少保留一个 PI 引脚用于测试;

- 若有更多可用引脚, 亦可使用;

- 所有时钟必须由 PI 引脚控制;

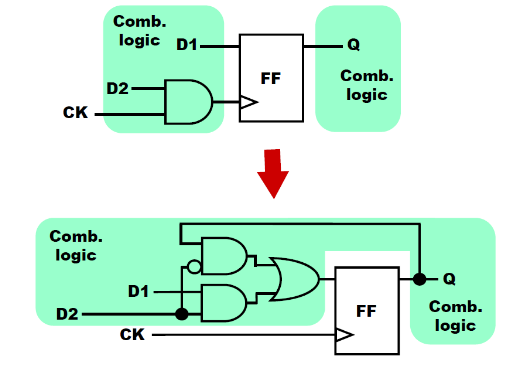

- 时钟信号不得馈入触发器的数据输入端。

1.2.1.2. 纠正规则违规

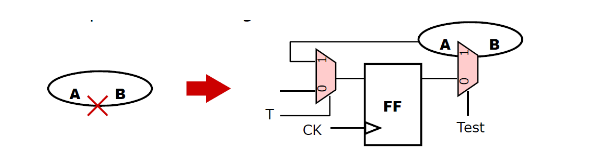

所有时钟必须由 PIs 控制

添加扫描触发器和多路复用器可以打开反馈回路以便进行测试

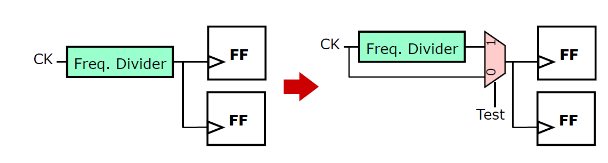

测试派生时钟需要使用多路复用器来绕过分频级

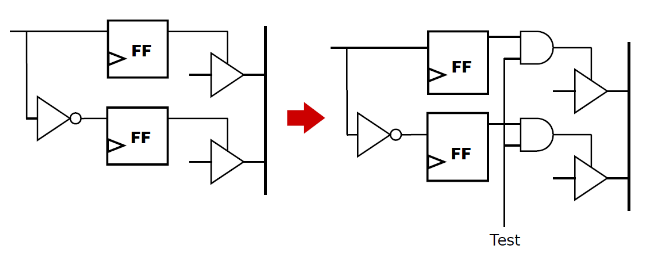

与门防止总线驱动器在测试期间被正常逻辑激活;

1.2.1.3. 流程

- 步骤 1: 切换到移位寄存器(SR)模式, 并通过移入交替的 1 和 0 序列 (例如 00110 ) 来检查 SR操作 (功能测试)

- 步骤 2: 初始化 SR,加载第一个模式

- 步骤 3: 返回正常模式并应用测试图样

- 步骤 4: 切换到 SR 模式, 移出最终状态, 同时为下一次测试设置起始状态。转至步骤 3。

1.2.1.4. 组合测试向量

1.2.1.5. 测试扫描寄存器

1.2.1.6. 多扫描寄存器

1.2.1.7. 层次扫描

1.2.1.8. 最佳扫描布局

1.2.1.9. 自动化扫描设计

1.2.1.10. DFT 编译器流程示例

1.2.1.10.1. 移位寄存器

1.2.2. 部分扫描

1.2.3. 伴随子可测试设计

伴随子(Syndrome):布尔函数中“1”的比例,即

其中

可测性条件:若电路存在故障

实现方法

- 定理:两级无冗余单边(Unate)电路天然具备综合症可测性。

- 通用修正:通过添加控制输入(如AND门控制信号),使非单边电路可测。

- 示例:

,添加控制信号后变成 ,保证 。

- 示例:

2. 内置自检 Built-In Self-Test,BIST

BIST,就是芯片内置的自我测试的能力。

BIST 的优势在于:

- 测试模式在芯片上生成,可控性提升;

- 片上评估的响应,可观察性增加;

- 测试可在线 ( 并发 ) 或离线进行;

- 测试能以电路全速运行,更真实,测试时间更短;

- 延迟测试更简便,外部测试设备极大简化, 甚至完全省去

- 易于适应工程变更

2.1. 在线与离线 BIST

在线 BIST

- 并发(EDAC、NMR、完全自检检查器等):

- 编码或模块化冗余技术(容错)

- 即时纠正由临时或永久故障引起的错误

- 非并发(诊断程序):在系统处于空闲状态时执行

BIST组件

- 测试模式生成器(TPG):

- 伪随机生成器(PRPG):如线性反馈移位寄存器(LFSR)。

- 特征多项式:定义LFSR的反馈结构,决定生成序列的周期。

- 响应分析器:

- 签名分析(Signature Analysis):利用LFSR压缩响应,生成唯一签名。

- 其他技术:奇偶校验、1计数、转换计数等。

2.2. 签名分析

2.3. 伪随机模式生成器 PRPG

2.4. 内置逻辑模块观察器 BILBO

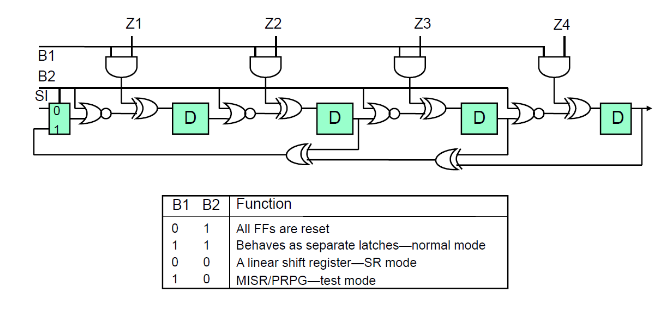

BILBO 是一种多功能测试模块, 既可作为测试生成器, 也可用作特征分析仪。它由一排触发器 ( FFs ) 及若干用于移位和反馈操作的附加门电路构成。