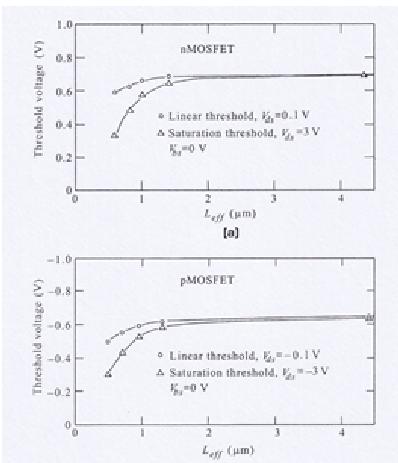

短沟道效应是指随着沟道长度

短沟道效应的后果:

- 可能导致器件漏电流和功耗增加。

- 芯片上的最小几何器件必须根据短沟道效应进行设计。

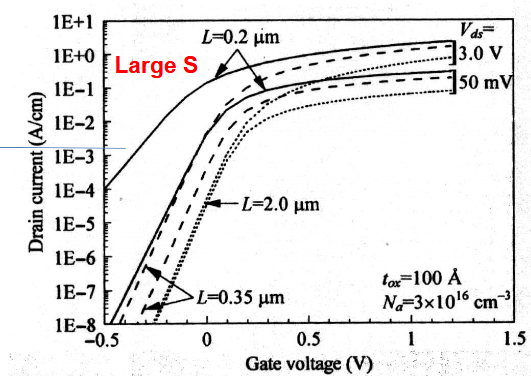

短沟道 MOSFET 中的亚阈值电流,可以看出当 L 减小到 0.2

短沟道效应的物理原因

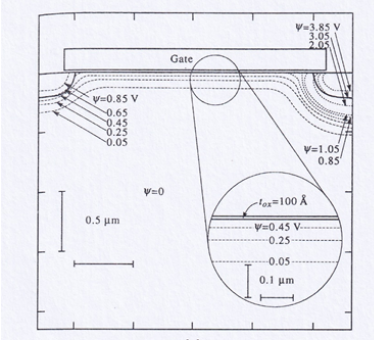

对于长沟道器件,模拟 2μm 器件主要沿 y 轴的等势(平行于 Si-SiO2 界面)。电场仅在 x 方向上变化, y 方向的变化最小(近似看作一维场,纵向上的电场变化可以忽略)。

这里可以看出,沿着沟道的电子电势基本是和沟道长度相当且平稳的(仅仅在接近源端和漏端处呈现二维电场)。

这里可以看出,沿着沟道的电子电势基本是和沟道长度相当且平稳的(仅仅在接近源端和漏端处呈现二维电场)。

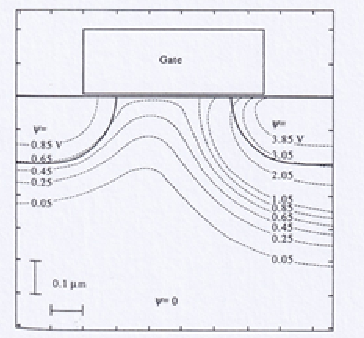

对于短沟道器件,对于相同的 Vg 和 Vds,等电位线更呈曲线状。电场是二维的。 Si 表面的能带弯曲更大,耗尽区更宽。器件具有较低的阈值电压。

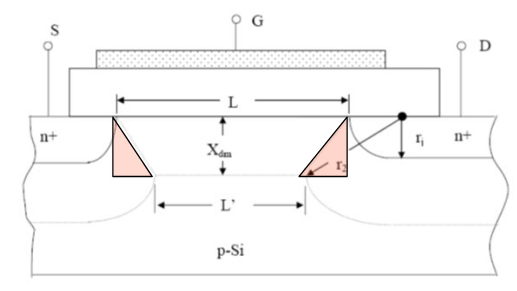

二维场图案是由于源极和漏极靠近而产生的。每个形成一个 p-n 结并具有相关的耗尽区。对于长沟道情况,这些耗尽区相距足够远,不会影响器件中的场图案。对于短沟道情况,源极-漏极的间隔与 MOS 耗尽宽度相当,因此场图案受源极漏极电压的强烈影响。

二维场图案是由于源极和漏极靠近而产生的。每个形成一个 p-n 结并具有相关的耗尽区。对于长沟道情况,这些耗尽区相距足够远,不会影响器件中的场图案。对于短沟道情况,源极-漏极的间隔与 MOS 耗尽宽度相当,因此场图案受源极漏极电压的强烈影响。

解释模型

用来解释这个现象的主要有两个模型:

- 电荷共享

- 漏致势垒降低(DIBL)

电荷共享

阈值电压可以表示为,

对于长沟道器件,对阈值有影响的总电荷约为

传统长沟道模型假设栅极完全控制其下方的耗尽区电荷

所以栅极实际控制的电荷为,

由此能推导出

假设有

随后用几何关系来表示

随后再表示阈值电压,

这里我们定义电荷共享系数

电荷共享系数定义式

指向原始笔记的链接

电荷共享模型的问题

电荷共享实际上不能通过定量计算的方式与实际测量阈值电压结果符合。主要问题有下,

- 电荷被任意分配,而非通过泊松方程进行数值积分计算;

- 忽略了漏极电压

对沟道电势的影响。 由此又提出了漏致势垒降低(drain induced barrier lowering, DIBL)模型。

漏致势垒降低

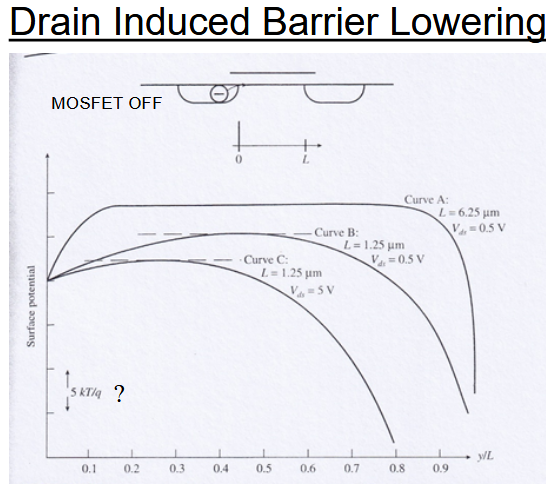

该图显示了表面电势(对于电子)作为归一化距离 y/L 的函数。在源极 (y/L=0) 处,当器件关闭时,表面势垒可防止电子进入沟道区域。对于长沟道情况(曲线 A),大部分沟道上的势垒是平坦且均匀的。对于短沟道情况(曲线 B、C),势垒较低且更圆。如果漏极偏压增加,势垒会进一步降低 (DIBL)。降低的势垒增加了电子进入通道的可能性并导致阈值电压降低。

该图显示了表面电势(对于电子)作为归一化距离 y/L 的函数。在源极 (y/L=0) 处,当器件关闭时,表面势垒可防止电子进入沟道区域。对于长沟道情况(曲线 A),大部分沟道上的势垒是平坦且均匀的。对于短沟道情况(曲线 B、C),势垒较低且更圆。如果漏极偏压增加,势垒会进一步降低 (DIBL)。降低的势垒增加了电子进入通道的可能性并导致阈值电压降低。

具有均匀掺杂密度的 nMOSFET 耗尽区的电场由下式给出:

注:

模拟横向场与耗尽区距离 y 的关系

注:对于 (a),横向场随距离呈指数减小。这种指数衰减的特征长度不随沟道长度而改变。因此,短沟道器件中间的横向场强于长沟道器件。施加漏极偏压将零场点移向源极。零场点对应于 DIBL 中的潜在最大值点。

注:对于 (a),横向场随距离呈指数减小。这种指数衰减的特征长度不随沟道长度而改变。因此,短沟道器件中间的横向场强于长沟道器件。施加漏极偏压将零场点移向源极。零场点对应于 DIBL 中的潜在最大值点。