[! tldr] 翻到 work example 开始看。

1. CMOS 制造

2. 金属化

2.1. 先进金属化

2.1.1. 双大马士革工艺

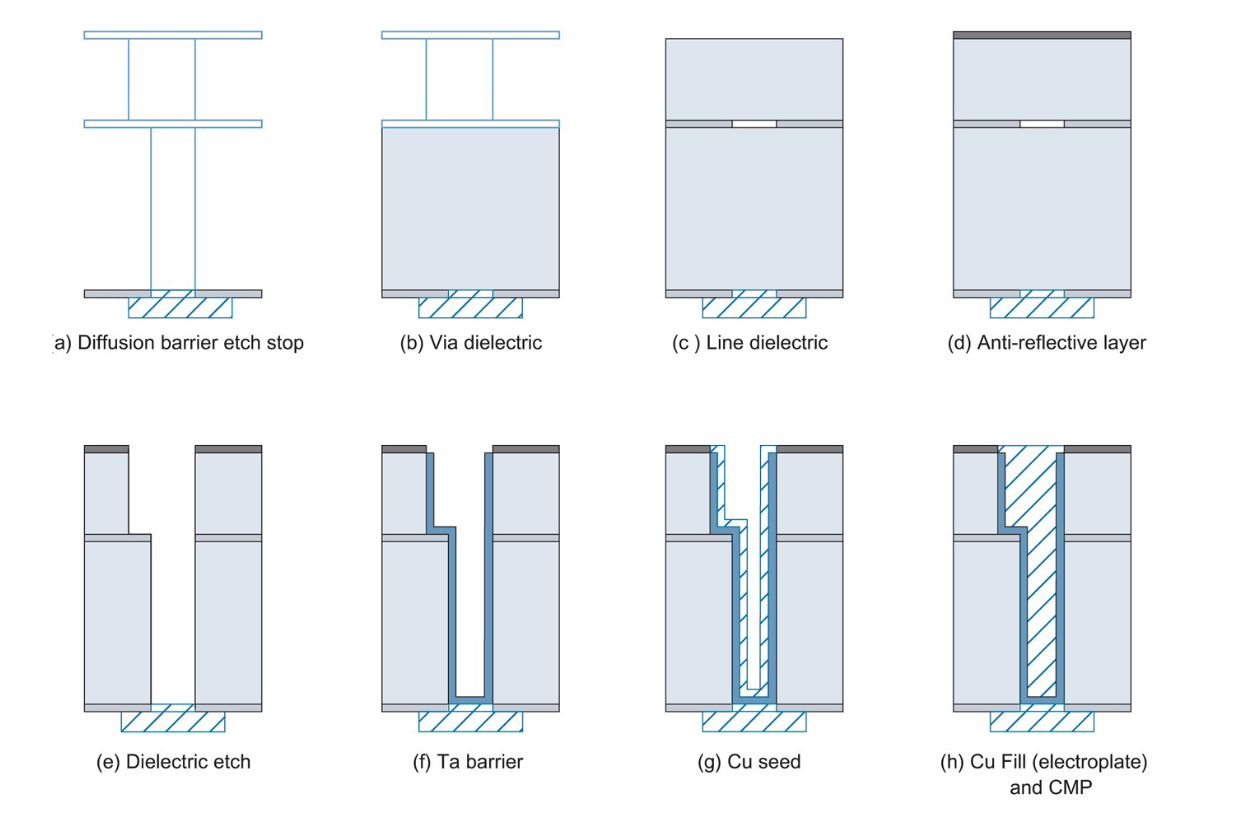

这一个工艺的关键就是通过两次蚀刻制造一个 stud。

图中的 “Ta” 是指钽 (Tantalum),它通常用作铜互连工艺中的扩散阻挡层。钽具有良好的化学稳定性和耐腐蚀性,能够防止铜原子扩散到周围的介质中。钽或钽氮化物(TaN)常作为铜布线的扩散阻挡层,确保铜不会扩散到低介电常数材料中,导致电路性能退化或失效。

在图中,“Ta barrier” 指的就是这种钽阻挡层,位于金属通孔或导线结构的周围,用于隔离铜和其他材料。

2.1.2. 制造服务

2.1.2.1. 教育服务

- 美国:MOSIS

- EC:EuroPractice

- 台湾:国家芯片实施中心 (CIC)

- 日本:VLSI 设计和教育中心 (VDEC),位于东京大学,于 1996 年开发

2.1.2.2. 代工 = 出租生产

代工厂是当今晶圆厂产能的主要来源。

2.2. 工艺误差

- 光刻胶收缩、撕裂。

- 材料沉积的变化。

- 温度变化。

- 氧化物厚度的变化。

- 杂质。

- 批次之间的差异。

- 晶圆上的变化。

2.2.1. 制造过程中的问题

- 光刻胶收缩、撕裂。

- 材料沉积的变化。

- 温度变化。

- 氧化物厚度的变化。

- 杂质。

- 批次之间的差异。

- 晶圆上的变化。

2.2.2. 晶体管问题

- 阈值电压的变化:

- 氧化物厚度;

- 离子注入;

- 多晶硅变化。

- 源/漏扩散重叠的变化。

- 衬底的变化。

2.2.3. 连线问题

- 扩散:掺杂的变化 → 电阻、电容的变化。

- 多晶硅、金属:高度、宽度的变化 → 电阻、电容的变化。

- 短路和开路

2.2.4. 氧化物问题

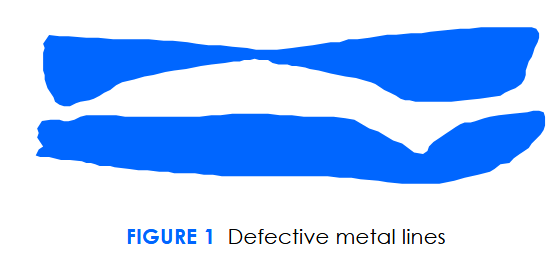

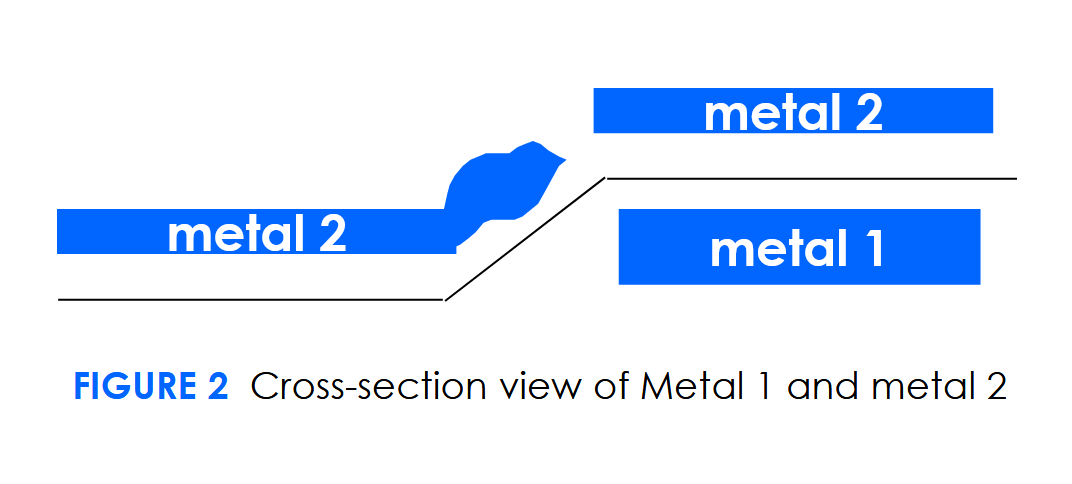

如果在高度上的变化太过陡峭,会导致金属层缺乏平面性,也叫台阶覆盖(step coverage)。

2.2.5. 通孔问题

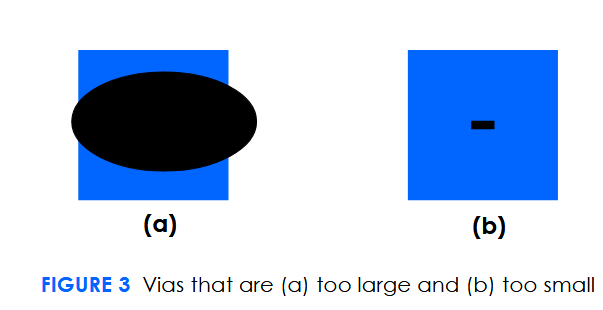

- 通孔尺寸不合适。太大容易造成短路(np 之间),太小则会导致电阻太大。

3. 版图设计规则

这里只介绍基础规则。

布局设计规则是用来设计掩膜,设计出来的掩膜定义了晶体管的最小尺寸,由此决定了速度、开销以及功耗。

特征尺寸(也叫单位尺寸)一般用

我们在表征规则的时候,用 Lambda 设计规则,即

布局规则的主要目标是在尽可能小的区域内构建可靠的功能电路。

[! tip] Slides 上的其他内容不用记,仅作了解。

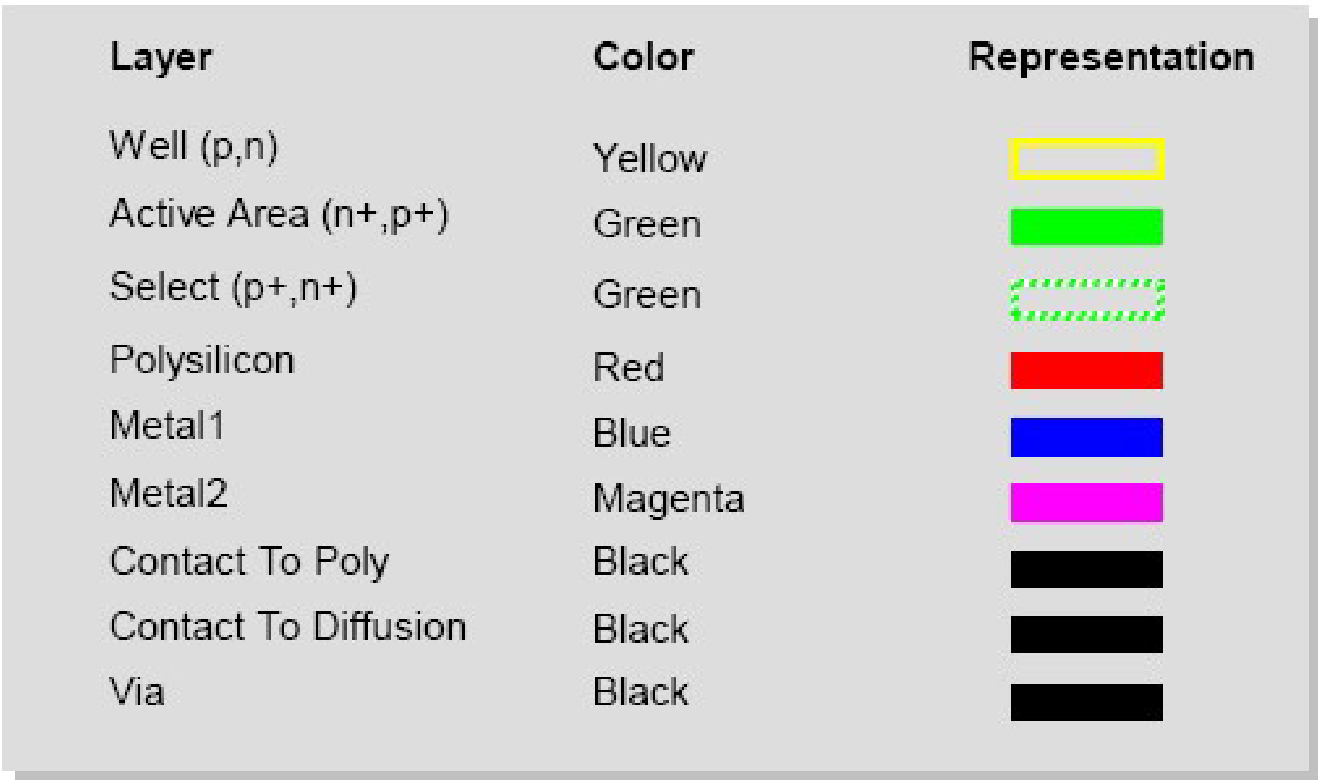

3.1. 典型 CMOS 工艺层

[! tip] Layer 相关内容都没必要记,只要能认出来就行。

3.2. 引入

了解以下的内容即可,

- lambda 设计规则

- 基础规则。

- 最小层宽度

- 最小层间距

- 最小层重叠

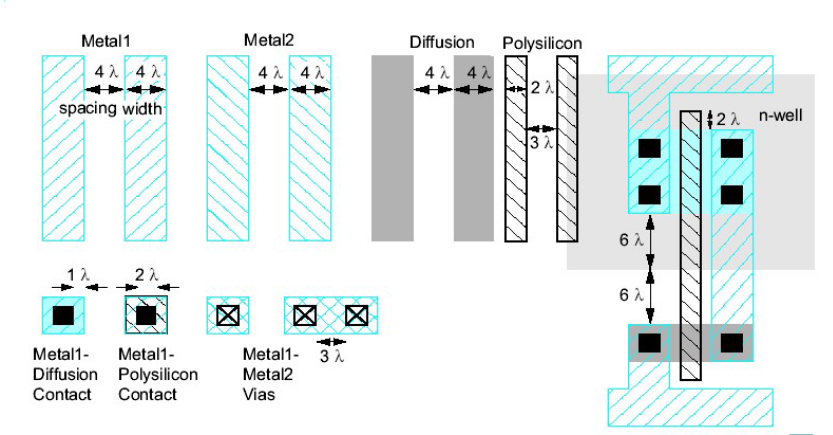

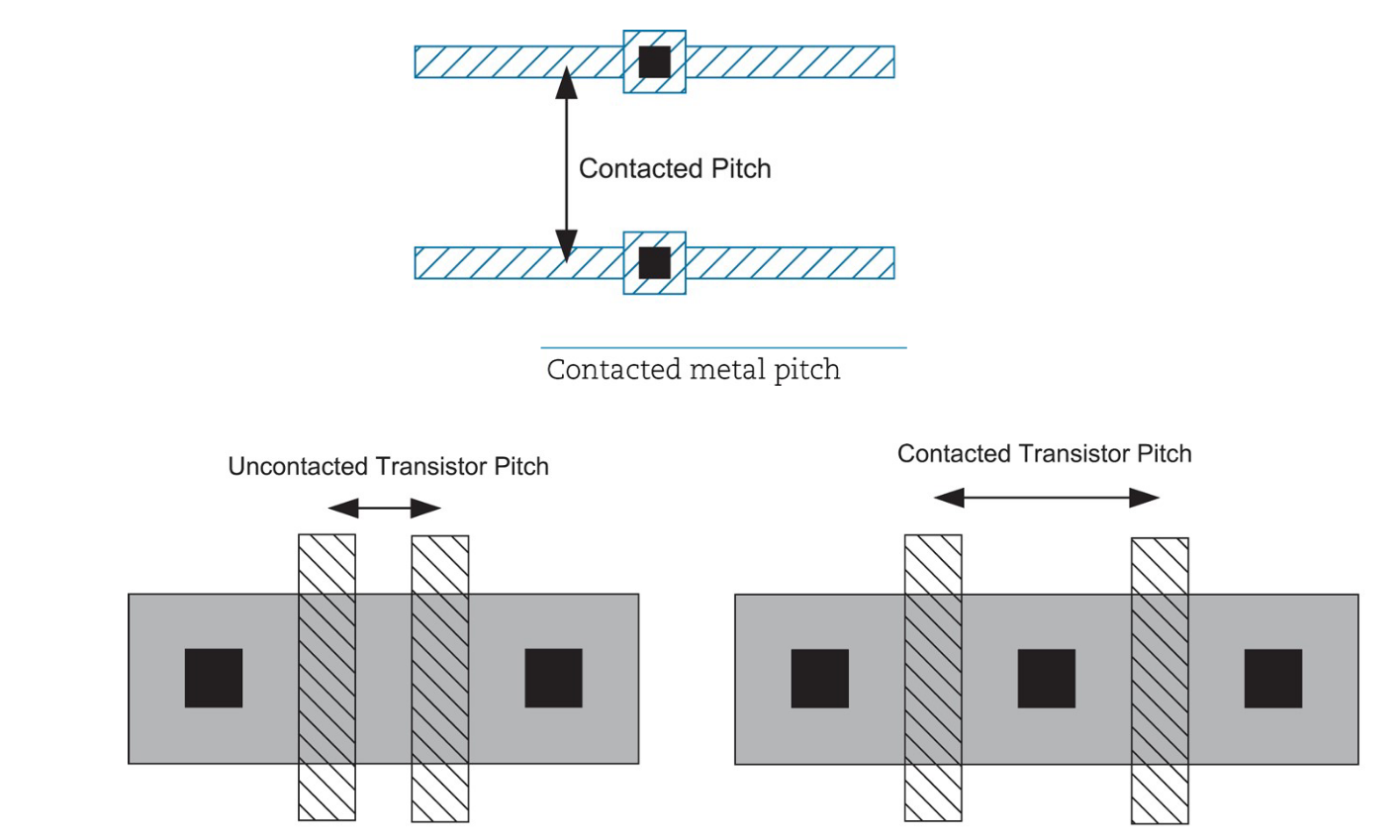

3.3. 简化的设计规则

这里看图记一下不同层的宽度和间距规则。

大致总结一下,只有 polysilicon 的宽度为

大致总结一下,只有 polysilicon 的宽度为

除了层本身,还有层之间的规则,例如超出重叠的位置需要有

3.4. 基础设计规则

3.5. 划线槽和其他结构

3.6. 玻璃罩

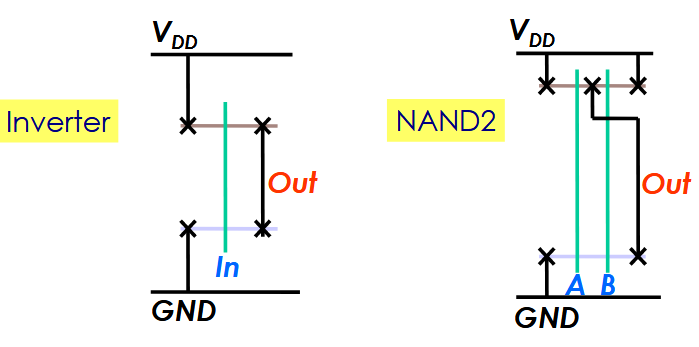

4. 棒状图

棒状图就是用简单的横线表示出所有组件或者通孔的相对位置。

这个很简单,先画出晶体管电路,然后再记住如何画串联和并联结构,以及哪些地方需要加通孔即可。

这个很简单,先画出晶体管电路,然后再记住如何画串联和并联结构,以及哪些地方需要加通孔即可。